# VS1003 - MP3/WMA AUDIO CODEC

#### **Features**

- Decodes MPEG 1 & 2 audio layer 3 (CBR & VBR); MP3+V;

WMA 4.0/4.1/7/8/9 all profiles;

WAV (PCM + IMA ADPCM);

General MIDI / SP-MIDI files

- Encodes IMA ADPCM from microphone or line input

- Streaming support for MP3 and WAV

- Operates with a single clock 12..13 MHz.

- Internal PLL clock multiplier

- Low-power operation

- High-quality stereo DAC with no phase error between channels

- 16-bit adjustable On-chip A/D converter

- Stereo earphone driver capable of driving a  $30\Omega$  load

- Separate operating voltages for analog, digital and I/O

- 7.5 KiB On-chip RAM for user code / data

- Serial control and data interfaces

- Can be used as a slave co-processor

- SPI flash boot for special applications

- UART for debugging purposes

- New functions may be added with software and 4 GPIO pins

#### **Description**

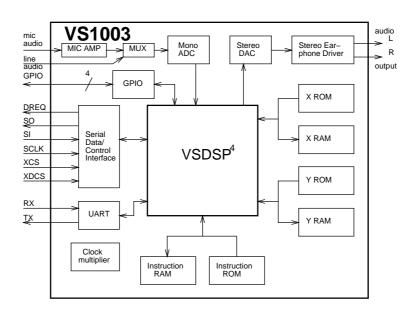

VS1003 is a single-chip MP3/WMA/MIDI audio decoder and ADPCM encoder. It contains a high-performance, proprietary low-power DSP processor core VS\_DSP<sup>4</sup>, working data memory, 5 KiB instruction RAM and 0.5 KiB data RAM for user applications, serial control and input data interfaces, 4 general purpose I/O pins, an UART, as well as a high-quality variable-sample-rate mono ADC and stereo DAC, followed by an earphone amplifier and a ground buffer.

VS1003 receives its input bitstream through a serial input bus, which it listens to as a system slave. The input stream is decoded and passed through a digital volume control to an 18-bit oversampling, multi-bit, sigma-delta DAC. The decoding is controlled via a serial control bus. In addition to the basic decoding, it is possible to add application specific features, like DSP effects, to the user RAM memory.

# **Contents**

| 1 | Lice  | nses                                             | 9  |

|---|-------|--------------------------------------------------|----|

| 2 | Disc  | laimer                                           | 9  |

| 3 | Defin | nitions                                          | 9  |

| 4 | Cha   | racteristics & Specifications                    | 10 |

|   | 4.1   | Analog Characteristics                           | 10 |

|   | 4.2   | Power Consumption                                | 10 |

|   | 4.3   | DAC Interpolation Filter Characteristics         | 11 |

|   | 4.4   | DAC Interpolation Filter Characteristics         | 11 |

|   | 4.5   | Absolute Maximum Ratings                         | 11 |

|   | 4.6   | Recommended Operating Conditions                 | 11 |

|   | 4.7   | Digital Characteristics                          | 12 |

|   | 4.8   | Switching Characteristics - Clocks               | 12 |

|   | 4.9   | Switching Characteristics - DREQ Signal          | 12 |

|   | 4.10  | Switching Characteristics - SPI Interface Output | 12 |

|   | 4.11  | Switching Characteristics - Boot Initialization  | 12 |

| 5 | Pack  | tages and Pin Descriptions                       | 13 |

|   | 5.1   | Packages                                         | 13 |

|   |       | 5.1.1 LQFP-48                                    | 13 |

|   |       | 5.1.2 BGA-49                                     | 13 |

|   | 5.2   | LQFP-48 and BGA-49 Pin Descriptions              | 14 |

| 6 | Con   | nection Diagram, LQFP-48                         | 16 |

| CONTENTS |

|----------|

|          |

| 7 | SPI | Buses     |                                             | 17 |

|---|-----|-----------|---------------------------------------------|----|

|   | 7.1 | General   |                                             | 17 |

|   | 7.2 | SPI Bus   | s Pin Descriptions                          | 17 |

|   |     | 7.2.1     | VS1002 Native Modes (New Mode)              | 17 |

|   |     | 7.2.2     | VS1001 Compatibility Mode                   | 17 |

|   | 7.3 | Data Re   | equest Pin DREQ                             | 18 |

|   | 7.4 | Serial P  | Protocol for Serial Data Interface (SDI)    | 18 |

|   |     | 7.4.1     | General                                     | 18 |

|   |     | 7.4.2     | SDI in VS1002 Native Modes (New Mode)       | 18 |

|   |     | 7.4.3     | SDI in VS1001 Compatibility Mode            | 19 |

|   |     | 7.4.4     | Passive SDI Mode                            | 19 |

|   | 7.5 | Serial P  | Protocol for Serial Command Interface (SCI) | 19 |

|   |     | 7.5.1     | General                                     | 19 |

|   |     | 7.5.2     | SCI Read                                    | 20 |

|   |     | 7.5.3     | SCI Write                                   | 20 |

|   | 7.6 | SPI Tim   | ning Diagram                                | 21 |

|   | 7.7 | SPI Exa   | amples with SM_SDINEW and SM_SDISHARED set  | 22 |

|   |     | 7.7.1     | Two SCI Writes                              | 22 |

|   |     | 7.7.2     | Two SDI Bytes                               | 22 |

|   |     | 7.7.3     | SCI Operation in Middle of Two SDI Bytes    | 23 |

| 8 | Fun | ctional D | Description                                 | 24 |

|   | 8.1 | Main Fe   | eatures                                     | 24 |

|   | 8.2 | Support   | ted Audio Codecs                            | 24 |

|   |     | 8.2.1     | Supported MP3 (MPEG layer 3) Formats        | 24 |

# **VS1003 PRELIMINARY**

|     | 8.2.2    | Supported WMA Formats       | . 25 |

|-----|----------|-----------------------------|------|

|     | 8.2.3    | Supported RIFF WAV Formats  | . 26 |

|     | 8.2.4    | Supported MIDI Formats      | . 26 |

| 8.3 | Data F   | Flow of VS1003              | . 27 |

| 8.4 | Serial 1 | Data Interface (SDI)        | . 27 |

| 8.5 | Serial   | Control Interface (SCI)     | . 28 |

| 8.6 | SCI Re   | egisters                    | . 28 |

|     | 8.6.1    | SCI_MODE (RW)               | . 29 |

|     | 8.6.2    | SCI_STATUS (RW)             | . 31 |

|     | 8.6.3    | SCI_BASS (RW)               | . 31 |

|     | 8.6.4    | SCI_CLOCKF (RW)             | . 32 |

|     | 8.6.5    | SCI_DECODE_TIME (RW)        | . 33 |

|     | 8.6.6    | SCI_AUDATA (RW)             | . 33 |

|     | 8.6.7    | SCI_WRAM (RW)               | . 33 |

|     | 8.6.8    | SCI_WRAMADDR (W)            | . 33 |

|     | 8.6.9    | SCI_HDAT0 and SCI_HDAT1 (R) | . 34 |

|     | 8.6.10   | SCI_AIADDR (RW)             | . 35 |

|     | 8.6.11   | SCI_VOL (RW)                | . 35 |

|     | 8.6.12   | SCI_AICTRL[x] (RW)          | . 36 |

| 8.7 | Stereo   | Audio DAC                   | . 36 |

| Ope | ration   |                             | 37   |

| 9.1 | Clocki   | ing                         | . 37 |

| 9.2 | Hardw    | vare Reset                  | . 37 |

| 9.3 | Softwa   | are Reset                   | . 37 |

9

|    | 9.4   | SPI Boot                       | 38         |

|----|-------|--------------------------------|------------|

|    | 9.5   | Play/Decode                    | 38         |

|    | 9.6   | Feeding PCM data               | 38         |

|    | 9.7   | SDI Tests                      | 39         |

|    |       | 9.7.1 Sine Test                | 39         |

|    |       | 9.7.2 Pin Test                 | 39         |

|    |       | 9.7.3 Memory Test              | 40         |

|    |       | 9.7.4 SCI Test                 | 40         |

| 10 | VS10  | 003 Registers                  | <b>4</b> 1 |

|    | 10.1  | Who Needs to Read This Chapter | 41         |

|    | 10.2  | The Processor Core             | 41         |

|    | 10.3  | VS1003 Memory Map              | 41         |

|    | 10.4  | SCI Registers                  | 41         |

|    | 10.5  | Serial Data Registers          | 42         |

|    | 10.6  | DAC Registers                  | 43         |

|    | 10.7  | GPIO Registers                 | 43         |

|    | 10.8  | Interrupt Registers            | 44         |

|    | 10.9  | A/D Modulator Registers        | 45         |

|    | 10.10 | OWatchdog v1.0 2002-08-26      | 46         |

|    |       | 10.10.1 Registers              | 46         |

|    | 10.11 | UART v1.0 2002-04-23           | 47         |

|    |       | 10.11.1 Registers              | 47         |

|    |       | 10.11.2 Status UARTx_STATUS    | 47         |

|    |       | 10.11.3 Data UARTx DATA        | 48         |

| 10.11.4 Data High UARTx_DATAH            | <br>48 |

|------------------------------------------|--------|

| 10.11.5 Divider UARTx_DIV                | <br>48 |

| 10.11.6 Interrupts and Operation         | <br>49 |

| 10.12Timers v1.0 2002-04-23              | <br>50 |

| 10.12.1 Registers                        | <br>50 |

| 10.12.2 Configuration TIMER_CONFIG       | <br>50 |

| 10.12.3 Configuration TIMER_ENABLE       | <br>51 |

| 10.12.4 Timer X Startvalue TIMER_Tx[L/H] | <br>51 |

| 10.12.5 Timer X Counter TIMER_TxCNT[L/H] | <br>51 |

| 10.12.6 Interrupts                       | <br>51 |

| 10.13System Vector Tags                  | <br>52 |

| 10.13.1 AudioInt, 0x20                   | <br>52 |

| 10.13.2 SciInt, 0x21                     | <br>52 |

| 10.13.3 DataInt, 0x22                    | <br>52 |

| 10.13.4 ModuInt, 0x23                    | <br>52 |

| 10.13.5 TxInt, 0x24                      | <br>53 |

| 10.13.6 RxInt, 0x25                      | <br>53 |

| 10.13.7 Timer0Int, 0x26                  | <br>53 |

| 10.13.8 Timer1Int, 0x27                  | <br>53 |

| 10.13.9 UserCodec, 0x0                   | <br>54 |

| 10.14System Vector Functions             | <br>54 |

| 10.14.1 WriteIRam(), 0x2                 | <br>54 |

| 10.14.2 ReadIRam(), 0x4                  | <br>54 |

| 10 14 3 DataBytes() 0x6                  | 54     |

|    |        | 10.14.4 GetDataByte(), 0x8                  | 55 |

|----|--------|---------------------------------------------|----|

|    |        | 10.14.5 GetDataWords(), 0xa                 | 55 |

|    |        | 10.14.6 Reboot(), 0xc                       | 55 |

| 11 | Docu   | ament Version Changes                       | 56 |

|    | 11.1   | Version 0.90, 2005-01-28                    | 56 |

|    | 11.2   | Version 0.80, 2005-01-11                    | 56 |

|    | 11.3   | Version 0.70, 2004-07-28                    | 56 |

|    | 11.4   | Initial version 0.62 for VS1003, 2003-03-19 | 56 |

| 12 | Cont   | act Information                             | 57 |

| Li | ist of | Figures                                     |    |

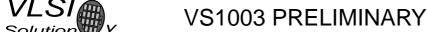

|    | 1      | Pin Configuration, LQFP-48                  | 13 |

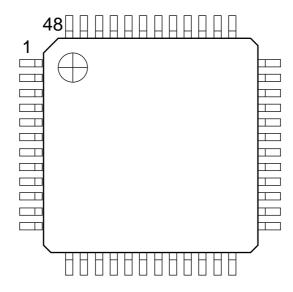

|    | 2      | Pin Configuration, BGA-49.                  | 13 |

|    | 3      | Typical Connection Diagram Using LQFP-48    | 16 |

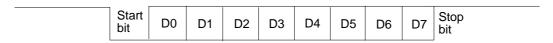

|    | 4      | BSYNC Signal - one byte transfer            | 19 |

|    | 5      | BSYNC Signal - two byte transfer            | 19 |

|    | 6      | SCI Word Read                               | 20 |

|    | 7      | SCI Word Write                              | 20 |

|    | 8      | SPI Timing Diagram                          | 21 |

|    | 9      | Two SCI Operations.                         | 22 |

|    | 10     | Two SDI Bytes                               | 22 |

|    | 11     | Two SDI Bytes Separated By an SCI Operation | 23 |

|    | 12     | Data Flow of VS1003                         | 27 |

#### LIST OF FIGURES

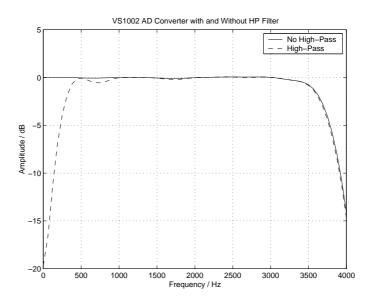

| 13 | ADPCM Frequency Responses with 8kHz sample rate | 30 |

|----|-------------------------------------------------|----|

| 14 | User's Memory Map                               | 42 |

| 15 | RS232 Serial Interface Protocol                 | 47 |

#### 1 Licenses

MPEG Layer-3 audio decoding technology licensed from Fraunhofer IIS and Thomson.

WMA technology licensed from Microsoft.

#### 2 Disclaimer

This is a *preliminary* datasheet. All properties and figures are subject to change.

#### 3 Definitions

ASIC Application Specific Integrated Circuit.

**B** Byte, 8 bits.

b Bit.

IC Integrated Circuit.

**Ki** "Kibi" =  $2^{10}$  = 1024 (IEC 60027-2).

**Mi** "Mebi" =  $2^{20}$  = 1048576 (IEC 60027-2).

VS\_DSP VLSI Solution's DSP core.

W Word. In VS\_DSP, instruction words are 32-bit and data words are 16-bit wide.

# VS1003 PRELIMINARY 4. CHARACTERISTICS & SPECIFICATIONS

#### **Characteristics & Specifications** 4

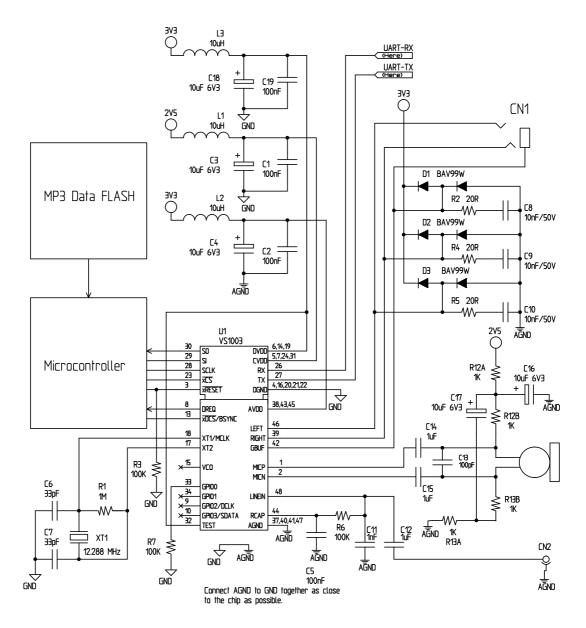

Unless otherwise noted: AVDD=2.7..3.6V, DVDD=2.0..2.7V, IOVDD=DVDD..3.6V, TA=-30..+85°C, XTALI=12.288MHz, Full-Scale Output Sinewave at 1.526 kHz, measurement bandwidth 20..20000 Hz, analog output load  $30\Omega$  (no ground buffer) or  $100\Omega$  (with ground buffer), MP3 bitstream 128 kbit/s. Local components as shown in Figure 3.

Note, that some analog values are in practice better than in these tables if chips are used within a limited temperature range and not too close to lower voltage limits.

#### **Analog Characteristics**

| Parameter                                       | Symbol | Min  | Тур       | Max  | Unit     |

|-------------------------------------------------|--------|------|-----------|------|----------|

| DAC Resolution                                  |        |      | 16        |      | bits     |

| Total Harmonic Distortion                       | THD    |      | 0.1       | 0.2  | %        |

| Dynamic Range (DAC unmuted, A-weighted)         | IDR    |      | 90        |      | dB       |

| S/N Ratio (full scale signal)                   | SNR    | 70   | 87        |      | dB       |

| Interchannel Isolation                          |        | 50   | 75        |      | dB       |

| Interchannel Gain Mismatch                      |        | -0.5 |           | 0.5  | dB       |

| Frequency Response                              |        | -0.1 |           | 0.1  | dB       |

| Frequency Response, AVDD = 2.7V                 |        | -0.3 |           | 0.3  | dB       |

| Full Scale Output Voltage (Peak-to-peak)        |        | 1.4  | $1.8^{1}$ | 2.0  | Vpp      |

| Deviation from Linear Phase                     |        |      |           | 5    | 0        |

| Out of Band Energy                              |        |      | -60       |      | dB       |

| Out of Band Energy with Analog Filter           |        |      | -90       |      | dB       |

| Analog Output Load Resistance, no ground buffer | AOLR1  | 16   | $30^{2}$  |      | Ω        |

| Analog Output Load Resistance, ground buffer    | AOLR2  | 16   | $100^{2}$ |      | Ω        |

| Analog Output Load Capacitance                  |        |      |           | 1000 | pF       |

| Microphone input amplifier gain                 | MICG   |      | 26        |      | dB       |

| Microphone input amplitude                      |        |      |           | 50   | mVrms AC |

| Line input amplitude                            |        |      |           | 1000 | mVrms AC |

| Line and Microphone input impedances            |        |      | 100       |      | kΩ       |

<sup>&</sup>lt;sup>1</sup> 3.6 volts can be achieved with +-to-+ wiring for mono difference sound.

#### 4.2 Power Consumption

| Parameter                                             | Symbol | Min | Тур               | Max               | Unit    |

|-------------------------------------------------------|--------|-----|-------------------|-------------------|---------|

| Power Supply Rejection                                |        |     | 40                |                   | dB      |

| Power Supply Consumption AVDD, Reset                  |        |     | 0.6               | 5.0               | $\mu$ A |

| Power Supply Consumption AVDD, no load                |        | 3.0 | 4.5               | 6.0               | mA      |

| Power Supply Consumption AVDD, output load $30\Omega$ |        | 4.0 | 5.5               | 40.0              | mA      |

| Power Supply Consumption AVDD, $30\Omega + GND$ -buf  |        | 6.0 | 7.5               | 40.0              | mA      |

| Power Supply Consumption DVDD = 2.5V, Reset           |        |     | 3.7               | 50.0              | $\mu$ A |

| Power Supply Consumption DVDD = 2.5V                  |        |     | 15.0 <sup>1</sup> | 32.0 <sup>2</sup> | mA      |

$<sup>^{1} 2.5 \</sup>times XTALI = 30.72 \text{ MHz}$

<sup>&</sup>lt;sup>2</sup> AOLR1/2 may be much lower, but below *Typical* distortion performance may be compromised.

<sup>&</sup>lt;sup>2</sup> 4.5×XTALI = 55.296 MHz, Maximum CPU/memory load

# VS1003 PRELIMINARY 4. CHARACTERISTICS & SPECIFICATIONS

# 4.3 DAC Interpolation Filter Characteristics

| Parameter                 | Symbol | Min      | Тур     | Max         | Unit |

|---------------------------|--------|----------|---------|-------------|------|

| Passband (to -3dB corner) |        | 0        |         | 0.459 Fs    | Hz   |

| Passband (Ripple Spec)    |        | 0        |         | 0.420 Fs    | Hz   |

| Passband Ripple           |        |          |         | $\pm 0.056$ | dB   |

| Transition Band           |        | 0.420 Fs |         | 0.580Fs     | Hz   |

| Stop Band                 |        | 0.580 Fs |         |             | Hz   |

| Stop Band Rejection       |        | 90       |         |             | dB   |

| Group Delay               |        |          | 15 / Fs |             | S    |

Fs is conversion frequency

#### 4.4 DAC Interpolation Filter Characteristics

| Parameter                   | Symbol | Min   | Тур | Max | Unit |

|-----------------------------|--------|-------|-----|-----|------|

| -3 dB bandwidth             |        | 300   |     |     | kHz  |

| Passband Response at 20 kHz |        | -0.05 |     |     | dB   |

### 4.5 Absolute Maximum Ratings

| Parameter                        | Symbol | Min  | Max                    | Unit |

|----------------------------------|--------|------|------------------------|------|

| Analog Positive Supply           | AVDD   | -0.3 | 3.6                    | V    |

| Digital Positive Supply          | DVDD   | -0.3 | 2.7                    | V    |

| I/O Positive Supply              | IOVDD  | -0.3 | 3.6                    | V    |

| Current at Any Digital Output    |        |      | ±50                    | mA   |

| Voltage at Any Digital Input     |        | -0.3 | IOVDD+0.3 <sup>1</sup> | V    |

| Operating Temperature            |        | -30  | +85                    | °C   |

| Functional Operating Temperature |        | -40  | +95                    | °C   |

| Storage Temperature              |        | -65  | +150                   | °C   |

<sup>&</sup>lt;sup>1</sup> Must not exceed 3.6 V

# **4.6 Recommended Operating Conditions**

| Parameter                          | Symbol    | Min  | Тур          | Max          | Unit |

|------------------------------------|-----------|------|--------------|--------------|------|

| Ambient Operating Temperature      |           | -30  |              | +85          | °C   |

| Analog and Digital Ground          | AGND DGND |      | 0.0          |              | V    |

| Positive Analog                    | AVDD      | 2.7  | 3.3          | 3.6          | V    |

| Positive Digital                   | DVDD      | 2.0  | 2.5          | 2.7          | V    |

| I/O Voltage                        | IOVDD     | DVDD | 3.3          | 3.6          | V    |

| Input Clock Frequency <sup>1</sup> | XTALI     | 12   | 12.288       | 13           | MHz  |

| Internal Clock Frequency           | CLKI      | 12   | 30.72        | 55.3         | MHz  |

| Internal Clock Multiplier          |           | 1.0× | $2.5 \times$ | $4.5 \times$ |      |

<sup>&</sup>lt;sup>1</sup> The maximum sample rate that can be played with correct speed is XTALI/256. Thus, XTALI must be at least 12.288 MHz to be able to play 48 kHz at correct speed.

# VS1003 PRELIMINARY 4. CHARACTERISTICS & SPECIFICATIONS

# **Digital Characteristics**

| Parameter                                            | Symbol | Min                | Тур | Max                    | Unit    |

|------------------------------------------------------|--------|--------------------|-----|------------------------|---------|

| High-Level Input Voltage                             |        | $0.7 \times IOVDD$ |     | IOVDD+0.3 <sup>1</sup> | V       |

| Low-Level Input Voltage                              |        | -0.2               |     | $0.3 \times IOVDD$     | V       |

| High-Level Output Voltage at $I_O = -2.0 \text{ mA}$ |        | $0.7 \times IOVDD$ |     |                        | V       |

| Low-Level Output Voltage at $I_O = 2.0 \text{ mA}$   |        |                    |     | $0.3 \times IOVDD$     | V       |

| Input Leakage Current                                |        | -1.0               |     | 1.0                    | $\mu$ A |

<sup>&</sup>lt;sup>1</sup> Must not exceed 3.6V

#### 4.8 Switching Characteristics - Clocks

| Parameter               | Symbol | Min | Тур    | Max | Unit |

|-------------------------|--------|-----|--------|-----|------|

| Master Clock Frequency  | XTALI  |     | 12.288 |     | MHz  |

| Master Clock Duty Cycle |        | 40  | 50     | 60  | %    |

| Clock Output            | XTALO  |     | XTALI  |     | MHz  |

# 4.9 Switching Characteristics - DREQ Signal

| Parameter           | Symbol | Min | Тур | Max | Unit |

|---------------------|--------|-----|-----|-----|------|

| Data Request Signal | DREQ   |     |     | 200 | ns   |

#### 4.10 Switching Characteristics - SPI Interface Output

| Parameter                 | Symbol | Min | Тур | Max              | Unit |

|---------------------------|--------|-----|-----|------------------|------|

| SPI Input Clock Frequency |        |     |     | $\frac{CLKI}{6}$ | MHz  |

| Rise time for SO          |        |     |     | 50               | ns   |

Note: Maximum load for SO is 100 pF.

#### **4.11** Switching Characteristics - Boot Initialization

| Parameter                         | Symbol | Min | Max         | Unit  |

|-----------------------------------|--------|-----|-------------|-------|

| XRESET active time                |        | 2   |             | XTALI |

| XRESET inactive to software ready |        |     | $16600^{1}$ | XTALI |

<sup>&</sup>lt;sup>1</sup> DREQ rises when initialization is complete. You should not send any data or commands before that.

# 5 Packages and Pin Descriptions

### 5.1 Packages

#### 5.1.1 LQFP-48

Figure 1: Pin Configuration, LQFP-48.

LQFP-48 package dimensions are at http://www.vlsi.fi/vs1001/lqfp48.pdf.

#### 5.1.2 BGA-49

Figure 2: Pin Configuration, BGA-49.

BGA-49 package dimensions are at http://www.vlsi.fi/vs1001/bga49.pdf.

# 5.2 LQFP-48 and BGA-49 Pin Descriptions

| Pin Name                   | LQFP-  | BGA49 | Pin   | Function                                                                        |

|----------------------------|--------|-------|-------|---------------------------------------------------------------------------------|

|                            | 48 Pin | Ball  | Type  |                                                                                 |

| MICP                       | 1      | C3    | AI    | microphone input                                                                |

| MICN                       | 2      | C2    | AI    | microphone input                                                                |

| XRESET                     | 3      | B1    | DI    | active low asynchronous reset                                                   |

| DGND0                      | 4      | D2    | DPWR  | digital & I/O ground                                                            |

| DVDD0                      | 5      | C1    | DPWR  | digital power supply                                                            |

| IOVDD0                     | 6      | D3    | IOPWR | I/O power supply                                                                |

| DVDD1                      | 7      | D1    | DPWR  | digital power supply                                                            |

| DREQ                       | 8      | E2    | DO    | data request, input bus                                                         |

| GPIO2 / DCLK <sup>1</sup>  | 9      | E1    | DIO   | general purpose IO 2 / serial input data bus clock                              |

| GPIO3 / SDATA <sup>1</sup> | 10     | F2    | DIO   | general purpose IO 3 / serial data input                                        |

| XDCS/BSYNC <sup>1</sup>    | 13     | E3    | DI    | data chip select / byte sync                                                    |

| IOVDD1                     | 14     | F3    | IOPWR | I/O power supply                                                                |

| VCO                        | 15     | G2    | DO    | clock VCO output                                                                |

| DGND1                      | 16     | F4    | DPWR  | digital & I/O ground                                                            |

| XTALO                      | 17     | G3    | AO    | crystal output                                                                  |

| XTALI                      | 18     | E4    | AI    | crystal input                                                                   |

| IOVDD2                     | 19     | G4    | IOPWR | I/O power supply                                                                |

| IOVDD3                     |        | F5    | IOPWR | I/O power supply                                                                |

| DGND2                      | 20     |       | DPWR  | digital & I/O ground                                                            |

| DGND3                      | 21     | G5    | DPWR  | digital & I/O ground                                                            |

| DGND4                      | 22     | F6    | DPWR  | digital & I/O ground                                                            |

| XCS                        | 23     | G6    | DI    | chip select input (active low)                                                  |

| DVDD2                      | 24     | G7    | DPWR  | digital power supply                                                            |

| RX                         | 26     | E6    | DI    | UART receive                                                                    |

| TX                         | 27     | F7    | DO    | UART transmit                                                                   |

| SCLK                       | 28     | D6    | DI    | clock for serial bus                                                            |

| SI                         | 29     | E7    | DI    | serial input                                                                    |

| SO                         | 30     | D5    | DO3   | serial output                                                                   |

| DVDD3                      | 31     | D7    | DPWR  | digital power supply                                                            |

| TEST                       | 32     | C6    | DI    | reserved for test, connect to IOVDD                                             |

| GPIO0                      | 33     | C7    | DIO   | general purpose IO 0, use $100 \text{ k}\Omega$ pull-down resistor <sup>2</sup> |

| GPIO1                      | 34     | B6    | DIO   | general purpose IO 1                                                            |

| AGND0                      | 37     | C5    | APWR  | analog ground, low-noise reference                                              |

| AVDD0                      | 38     | B5    | APWR  | analog power supply                                                             |

| RIGHT                      | 39     | A6    | AO    | right channel output                                                            |

| AGND1                      | 40     | B4    | APWR  | analog ground                                                                   |

| AGND2                      | 41     | A5    | APWR  | analog ground                                                                   |

| GBUF                       | 42     | C4    | AO    | ground buffer                                                                   |

| AVDD1                      | 43     | A4    | APWR  | analog power supply                                                             |

| RCAP                       | 44     | В3    | AIO   | filtering capacitance for reference                                             |

| AVDD2                      | 45     | A3    | APWR  | analog power supply                                                             |

| LEFT                       | 46     | B2    | AO    | left channel output                                                             |

| AGND3                      | 47     | A2    | APWR  | analog ground                                                                   |

| LINEIN                     | 48     | A1    | AI    | line input                                                                      |

<sup>&</sup>lt;sup>1</sup> First pin function is active in New Mode, latter in Compatibility Mode.

$<sup>^{2}</sup>$  Unless pull-down resistor is used, SPI Boot is tried. See Chapter 9.4 for details.

# Pin types:

| Type | Description                                |

|------|--------------------------------------------|

| DI   | Digital input, CMOS Input Pad              |

| DO   | Digital output, CMOS Input Pad             |

| DIO  | Digital input/output                       |

| DO3  | Digital output, CMOS Tri-stated Output Pad |

| AI   | Analog input                               |

| Type  | Description              |

|-------|--------------------------|

| AO    | Analog output            |

| AIO   | Analog input/output      |

| APWR  | Analog power supply pin  |

| DPWR  | Digital power supply pin |

| IOPWR | I/O power supply pin     |

In BGA-49, no-connect balls are A7, B7, D4, E5, F1, G1. In LQFP-48, no-connect pins are 11, 12, 25, 35, 36.

#### 6 Connection Diagram, LQFP-48

Figure 3: Typical Connection Diagram Using LQFP-48.

The ground buffer GBUF can be used for common voltage (1.24 V) for earphones. This will eliminate the need for large isolation capacitors on line outputs, and thus the audio output pins from VS1003 may be connected directly to the earphone connector.

If GBUF is not used, LEFT and RIGHT must be provided with 100  $\mu$ F capacitors.

If UART is not used, RX should connect to IOVDD and TX be unconnected. U2 and CN2 are not needed.

Note: This connection assumes SM\_SDINEW is active (see Chapter 8.6.1). If also SM\_SDISHARE is used, xDCS doesn't need to be connected (see Chapter 7.2.1).

#### 7 SPI Buses

#### 7.1 General

The SPI Bus - that was originally used in some Motorola devices - has been used for both VS1003's Serial Data Interface SDI (Chapters 7.4 and 8.4) and Serial Control Interface SCI (Chapters 7.5 and 8.5).

#### 7.2 SPI Bus Pin Descriptions

#### 7.2.1 VS1002 Native Modes (New Mode)

These modes are active on VS1003 when SM\_SDINEW is set to 1 (default at startup). DCLK, SDATA and BSYNC are replaced with GPIO2, GPIO3 and XDCS, respectively.

| SDI Pin | SCI Pin                                                                         | Description                                                                     |

|---------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| XDCS    | XCS Active low chip select input. A high level forces the serial interface into |                                                                                 |

|         |                                                                                 | standby mode, ending the current operation. A high level also forces serial     |

|         |                                                                                 | output (SO) to high impedance state. If SM_SDISHARE is 1, pin                   |

|         |                                                                                 | XDCS is not used, but the signal is generated internally by inverting           |

|         |                                                                                 | XCS.                                                                            |

| SC      | CK                                                                              | Serial clock input. The serial clock is also used internally as the master      |

| clock   |                                                                                 | clock for the register interface.                                               |

| SCK car |                                                                                 | SCK can be gated or continuous. In either case, the first rising clock edge     |

|         |                                                                                 | after XCS has gone low marks the first bit to be written.                       |

| S       | I                                                                               | Serial input. If a chip select is active, SI is sampled on the rising CLK edge. |

| -       | SO                                                                              | Serial output. In reads, data is shifted out on the falling SCK edge.           |

|         |                                                                                 | In writes SO is at a high impedance state.                                      |

#### 7.2.2 VS1001 Compatibility Mode

This mode is active when SM\_SDINEW is set to 0. In this mode, DCLK, SDATA and BSYNC are active.

| SDI Pin | SCI Pin | Description                                                                 |

|---------|---------|-----------------------------------------------------------------------------|

| -       | XCS     | Active low chip select input. A high level forces the serial interface into |

|         |         | standby mode, ending the current operation. A high level also forces serial |

|         |         | output (SO) to high impedance state.                                        |

| BSYNC   | -       | SDI data is synchronized with a rising edge of BSYNC.                       |

| DCLK    | SCK     | Serial clock input. The serial clock is also used internally as the master  |

|         |         | clock for the register interface.                                           |

|         |         | SCK can be gated or continuous. In either case, the first rising clock edge |

|         |         | after XCS has gone low marks the first bit to be written.                   |

| SDATA   | SI      | Serial input. SI is sampled on the rising SCK edge, if XCS is low.          |

| -       | SO      | Serial output. In reads, data is shifted out on the falling SCK edge.       |

|         |         | In writes SO is at a high impedance state.                                  |

#### 7.3 Data Request Pin DREQ

The DREQ pin/signal is used to signal if VS1003's FIFO is capable of receiving data. If DREQ is high, VS1003 can take at least 32 bytes of SDI data or one SCI command. When these criteria are not met, DREQ is turned low, and the sender should stop transferring new data.

Because of the 32-byte safety area, the sender may send upto 32 bytes of SDI data at a time without checking the status of DREQ, making controlling VS1003 easier for low-speed microcontrollers.

Note: DREQ may turn low or high at any time, even during a byte transmission. Thus, DREQ should only be used to decide whether to send more bytes. It should not abort a transmission that has already started.

Note: In VS10XX products upto VS1002, DREQ was only used for SDI. In VS1003 DREQ is also used to tell the status of SCI.

#### 7.4 Serial Protocol for Serial Data Interface (SDI)

#### 7.4.1 General

The serial data interface operates in slave mode so DCLK signal must be generated by an external circuit.

Data (SDATA signal) can be clocked in at either the rising or falling edge of DCLK (Chapter 8.6).

VS1003 assumes its data input to be byte-sychronized. SDI bytes may be transmitted either MSb or LSb first, depending of contents of SCI\_MODE (Chapter 8.6.1).

#### 7.4.2 SDI in VS1002 Native Modes (New Mode)

In VS1002 native modes (SM\_NEWMODE is 1), byte synchronization is achieved by XDCS. The state of XDCS may not change while a data byte transfer is in progress. To always maintain data synchronization even if there may be glitches in the boards using VS1003, it is recommended to turn XDCS every now and then, for instance once after every flash data block or a few kilobytes, just to keep sure the host and VS1003 are in sync.

If SM\_SDISHARE is 1, the XDCS signal is internally generated by inverting the XCS input.

For new designs, using VS1002 native modes are recommended.

#### 7.4.3 SDI in VS1001 Compatibility Mode

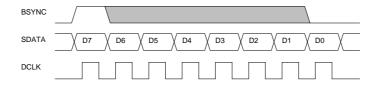

Figure 4: BSYNC Signal - one byte transfer.

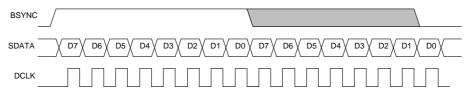

When VS1003 is running in VS1001 compatibility mode, a BSYNC signal must be generated to ensure correct bit-alignment of the input bitstream. The first DCLK sampling edge (rising or falling, depending on selected polarity), during which the BSYNC is high, marks the first bit of a byte (LSB, if LSB-first order is used, MSB, if MSB-first order is used). If BSYNC is '1' when the last bit is received, the receiver stays active and next 8 bits are also received.

Figure 5: BSYNC Signal - two byte transfer.

#### 7.4.4 Passive SDI Mode

If SM\_NEWMODE is 0 and SM\_SDISHARE is 1, the operation is otherwise like the VS1001 compatibility mode, but bits are only received while the BSYNC signal is '1'. Rising edge of BSYNC is still used for synchronization.

#### 7.5 Serial Protocol for Serial Command Interface (SCI)

#### 7.5.1 General

The serial bus protocol for the Serial Command Interface SCI (Chapter 8.5) consists of an instruction byte, address byte and one 16-bit data word. Each read or write operation can read or write a single register. Data bits are read at the rising edge, so the user should update data at the falling edge. Bytes are always send MSb first.

The operation is specified by an 8-bit instruction opcode. The supported instructions are read and write. See table below.

|       | Instruction |            |

|-------|-------------|------------|

| Name  | Opcode      | Operation  |

| READ  | 0b0000 0011 | Read data  |

| WRITE | 0b0000 0010 | Write data |

Note: VS1003 sets DREQ low after each SCI operation. The duration depends on the operation. It is not allowed to start a new SCI/SDI operation before DREQ is high again.

#### 7.5.2 SCI Read

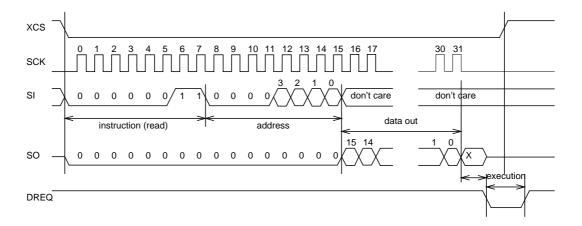

Figure 6: SCI Word Read

VS1003 registers are read from using the following sequence, as shown in Figure 6. First, XCS line is pulled low to select the device. Then the READ opcode (0x3) is transmitted via the SI line followed by an 8-bit word address. After the address has been read in, any further data on SI is ignored by the chip. The 16-bit data corresponding to the received address will be shifted out onto the SO line.

XCS should be driven high after data has been shifted out.

DREQ is driven low for a short while when in a read operation by the chip. This is a very short time and doesn't require special user attention.

#### **7.5.3** SCI Write

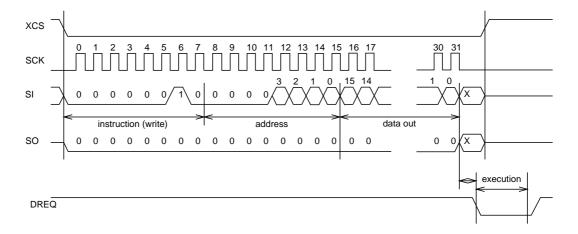

Figure 7: SCI Word Write

VS1003 registers are written from using the following sequence, as shown in Figure 7. First, XCS line is pulled low to select the device. Then the WRITE opcode (0x2) is transmitted via the SI line followed by an 8-bit word address.

After the word has been shifted in and the last clock has been sent, XCS should be pulled high to end the WRITE sequence.

After the last bit has been sent, DREQ is driven low for the duration of the register update, marked "execution" in the figure. The time varies depending on the register and its contents (see table in Chapter 8.6 for details). If the maximum time is longer than what it takes from the microcontroller to feed the next SCI command or SDI byte, it is not allowed to finish a new SCI/SDI operation before DREQ has risen up again.

#### 7.6 SPI Timing Diagram

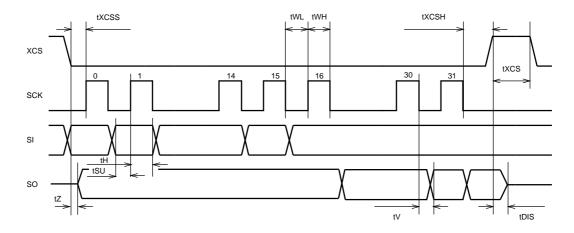

Figure 8: SPI Timing Diagram.

| Symbol | Min | Max                      | Unit        |

|--------|-----|--------------------------|-------------|

| tXCSS  | 5   |                          | ns          |

| tSU    | -26 |                          | ns          |

| tH     | 2   |                          | CLKI cycles |

| tZ     | 0   |                          | ns          |

| tWL    | 2   |                          | CLKI cycles |

| tWH    | 2   |                          | CLKI cycles |

| tV     |     | 2 (+ 25ns <sup>1</sup> ) | CLKI cycles |

| tXCSH  | -26 |                          | ns          |

| tXCS   | 2   |                          | CLKI cycles |

| tDIS   |     | 10                       | ns          |

<sup>&</sup>lt;sup>1</sup> 25ns is when pin loaded with 100pF capacitance. The time is shorter with lower capacitance.

Note: As tWL and tWH, as well as tH require at least 2 clock cycles, the maximum speed for the SPI bus that can easily be used is 1/6 of VS1003's internal clock speed CLKI. Slightly higher speed can be achieved with very careful timing tuning. For details, see Application Notes for VS10XX.

Note: Although the timing is derived from the internal clock CLKI, the system always starts up in  $1.0 \times$  mode, thus CLKI=XTALI.

Note: Negative numbers mean that the signal can change in different order from what is shown in the diagram.

#### 7.7 SPI Examples with SM\_SDINEW and SM\_SDISHARED set

#### 7.7.1 Two SCI Writes

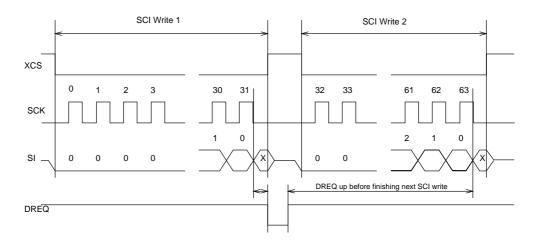

Figure 9: Two SCI Operations.

Figure 9 shows two consecutive SCI operations. Note that xCS *must* be raised to inactive state between the writes. Also DREQ must be respected as shown in the figure.

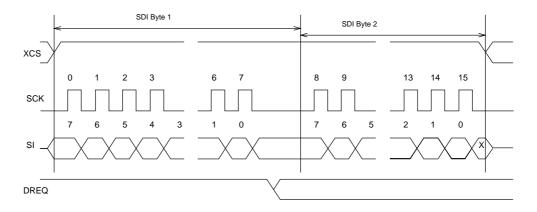

## 7.7.2 Two SDI Bytes

Figure 10: Two SDI Bytes.

SDI data is synchronized with a raising edge of xCS as shown in Figure 10. However, every byte doesn't need separate synchronization.

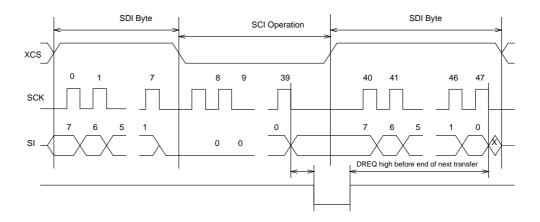

#### 7.7.3 SCI Operation in Middle of Two SDI Bytes

Figure 11: Two SDI Bytes Separated By an SCI Operation.

Figure 11 shows how an SCI operation is embedded in between SDI operations. xCS edges are used to synchronize both SDI and SCI. Remember to respect DREQ as shown in the figure.

# **8 Functional Description**

#### 8.1 Main Features

VS1003 is based on a proprietary digital signal processor, VS\_DSP. It contains all the code and data memory needed for MP3, WMA and WAV PCM + ADPCM audio decoding, MIDI synthesizer, together with serial interfaces, a multirate stereo audio DAC and analog output amplifiers and filters. Also AD-PCM audio encoding is supported using a microphone amplifier and A/D converter. A UART is provided for debugging purposes.

#### 8.2 Supported Audio Codecs

|      | Conventions                        |

|------|------------------------------------|

| Mark | Description                        |

| +    | Format is supported                |

| -    | Format exists but is not supported |

|      | Format doesn't exist               |

#### 8.2.1 Supported MP3 (MPEG layer 3) Formats

#### MPEG $1.0^{1}$ :

| Samplerate / Hz |    |    |    |    |    | F  | Bitrate | / kbit/ | 's  |     |     |     |     |     |

|-----------------|----|----|----|----|----|----|---------|---------|-----|-----|-----|-----|-----|-----|

|                 | 32 | 40 | 48 | 56 | 64 | 80 | 96      | 112     | 128 | 160 | 192 | 224 | 256 | 320 |

| 48000           | +  | +  | +  | +  | +  | +  | +       | +       | +   | +   | +   | +   | +   | +   |

| 44100           | +  | +  | +  | +  | +  | +  | +       | +       | +   | +   | +   | +   | +   | +   |

| 32000           | +  | +  | +  | +  | +  | +  | +       | +       | +   | +   | +   | +   | +   | +   |

#### MPEG 2.0<sup>1</sup>:

| Samplerate / Hz |   |    |    |    |    | F  | Bitrate | / kbit | /s |    |     |     |     |     |

|-----------------|---|----|----|----|----|----|---------|--------|----|----|-----|-----|-----|-----|

|                 | 8 | 16 | 24 | 32 | 40 | 48 | 56      | 64     | 80 | 96 | 112 | 128 | 144 | 160 |

| 24000           | + | +  | +  | +  | +  | +  | +       | +      | +  | +  | +   | +   | +   | +   |

| 22050           | + | +  | +  | +  | +  | +  | +       | +      | +  | +  | +   | +   | +   | +   |

| 16000           | + | +  | +  | +  | +  | +  | +       | +      | +  | +  | +   | +   | +   | +   |

#### MPEG 2.5<sup>1</sup> <sup>2</sup>:

| Samplerate / Hz |   |    |    |    |    | E  | Bitrate | / kbit/ | 's |    |     |     |     |     |

|-----------------|---|----|----|----|----|----|---------|---------|----|----|-----|-----|-----|-----|

|                 | 8 | 16 | 24 | 32 | 40 | 48 | 56      | 64      | 80 | 96 | 112 | 128 | 144 | 160 |

| 12000           | + | +  | +  | +  | +  | +  | +       | +       | +  | +  | +   | +   | +   | +   |

| 11025           | + | +  | +  | +  | +  | +  | +       | +       | +  | +  | +   | +   | +   | +   |

| 8000            | + | +  | +  | +  | +  | +  | +       | +       | +  | +  | +   | +   | +   | +   |

<sup>&</sup>lt;sup>1</sup> Also all variable bitrate (VBR) formats are supported.

<sup>&</sup>lt;sup>2</sup> Incompatibilities may occur because MPEG 2.5 is not a standard format.

#### **8.2.2** Supported WMA Formats

Windows Media Audio codec versions 2, 7, 8, and 9 are supported. All WMA profiles (L1, L2, and L3) are supported. Previously streams were separated into Classes 1, 2a, 2b, and 3. The decoder has passed Microsoft's conformance testing program.

#### WMA 4.0 / 4.1:

| Samplerate |   |   |   |    |    |    |    | Bitr | ate / k | bit/s |    |    |    |    |     |     |     |

|------------|---|---|---|----|----|----|----|------|---------|-------|----|----|----|----|-----|-----|-----|

| / Hz       | 5 | 6 | 8 | 10 | 12 | 16 | 20 | 22   | 32      | 40    | 48 | 64 | 80 | 96 | 128 | 160 | 192 |

| 8000       | + | + | + |    | +  |    |    |      |         |       |    |    |    |    |     |     |     |

| 11025      |   |   | + | +  |    |    |    |      |         |       |    |    |    |    |     |     |     |

| 16000      |   |   |   | +  | +  | +  | +  |      |         |       |    |    |    |    |     |     |     |

| 22050      |   |   |   |    |    | +  | +  | +    | +       |       |    |    |    |    |     |     |     |

| 32000      |   |   |   |    |    |    | +  | +    | +       | +     | +  | +  |    |    |     |     |     |

| 44100      |   |   |   |    |    |    |    |      | +       |       | +  | +  | +  | +  | +   | +   |     |

| 48000      |   |   |   |    |    |    |    |      |         |       |    |    |    |    | +   | +   |     |

#### WMA 7:

| Samplerate |   |   |   |    |    |    |    | Bitr | ate / k | bit/s |    |    |    |    |     |     |     |

|------------|---|---|---|----|----|----|----|------|---------|-------|----|----|----|----|-----|-----|-----|

| / Hz       | 5 | 6 | 8 | 10 | 12 | 16 | 20 | 22   | 32      | 40    | 48 | 64 | 80 | 96 | 128 | 160 | 192 |

| 8000       | + | + | + |    | +  |    |    |      |         |       |    |    |    |    |     |     |     |

| 11025      |   |   | + | +  |    |    |    |      |         |       |    |    |    |    |     |     |     |

| 16000      |   |   |   | +  | +  | +  | +  |      |         |       |    |    |    |    |     |     |     |

| 22050      |   |   |   |    |    | +  | +  | +    | +       |       |    |    |    |    |     |     |     |

| 32000      |   |   |   |    |    |    | +  |      | +       | +     | +  |    |    |    |     |     |     |

| 44100      |   |   |   |    |    |    |    |      | +       |       | +  | +  | +  | +  | +   | +   | +   |

| 48000      |   |   |   |    |    |    |    |      |         |       |    |    |    |    | +   | +   |     |

#### WMA 8:

| Samplerate |   |   |   |    |    |    |    | Bitr | ate / k | bit/s |    |    |    |    |     |     |     |

|------------|---|---|---|----|----|----|----|------|---------|-------|----|----|----|----|-----|-----|-----|

| / Hz       | 5 | 6 | 8 | 10 | 12 | 16 | 20 | 22   | 32      | 40    | 48 | 64 | 80 | 96 | 128 | 160 | 192 |

| 8000       | + | + | + |    | +  |    |    |      |         |       |    |    |    |    |     |     |     |

| 11025      |   |   | + | +  |    |    |    |      |         |       |    |    |    |    |     |     |     |

| 16000      |   |   |   | +  | +  | +  | +  |      |         |       |    |    |    |    |     |     |     |

| 22050      |   |   |   |    |    | +  | +  | +    | +       |       |    |    |    |    |     |     |     |

| 32000      |   |   |   |    |    |    | +  |      | +       | +     | +  |    |    |    |     |     |     |

| 44100      |   |   |   |    |    |    |    |      | +       |       | +  | +  | +  | +  | +   | +   | +   |

| 48000      |   |   |   |    |    |    |    |      |         |       |    |    |    |    | +   | +   | +   |

#### WMA 9:

| Samplerate |   |   |   |    |    |    |    |    | Bitı | rate / | kbit/s | ;  |    |    |     |     |     |     |     |

|------------|---|---|---|----|----|----|----|----|------|--------|--------|----|----|----|-----|-----|-----|-----|-----|

| / Hz       | 5 | 6 | 8 | 10 | 12 | 16 | 20 | 22 | 32   | 40     | 48     | 64 | 80 | 96 | 128 | 160 | 192 | 256 | 320 |

| 8000       | + | + | + |    | +  |    |    |    |      |        |        |    |    |    |     |     |     |     |     |

| 11025      |   |   | + | +  |    |    |    |    |      |        |        |    |    |    |     |     |     |     |     |

| 16000      |   |   |   | +  | +  | +  | +  |    |      |        |        |    |    |    |     |     |     |     |     |

| 22050      |   |   |   |    |    | +  | +  | +  | +    |        |        |    |    |    |     |     |     |     |     |

| 32000      |   |   |   |    |    |    | +  |    | +    | +      | +      |    |    |    |     |     |     |     |     |

| 44100      |   |   |   |    |    |    | +  |    | +    |        | +      | +  | +  | +  | +   | +   | +   | +   | +   |

| 48000      |   |   |   |    |    |    |    |    |      |        |        | +  |    | +  | +   | +   | +   |     |     |

In addition to these expected WMA decoding profiles, all other bitrate and samplerate combinations are supported, including variable bitrate WMA streams. Note that WMA does not consume the bitstream as evenly as MP3, so you need a higher peak transfer capability for clean playback at the same bitrate.

#### 8.2.3 Supported RIFF WAV Formats

The most common RIFF WAV subformats are supported.

| Format | Name              | Supported | Comments                                   |

|--------|-------------------|-----------|--------------------------------------------|

| 0x01   | PCM               | +         | 16 and 8 bits, any sample rate ≤ 48kHz     |

| 0x02   | ADPCM             | -         |                                            |

| 0x03   | IEEE_FLOAT        | -         |                                            |

| 0x06   | ALAW              | -         |                                            |

| 0x07   | MULAW             | -         |                                            |

| 0x10   | OKI_ADPCM         | -         |                                            |

| 0x11   | IMA_ADPCM         | +         | Any sample rate ≤ 48kHz                    |

| 0x15   | DIGISTD           | -         |                                            |

| 0x16   | DIGIFIX           | -         |                                            |

| 0x30   | DOLBY_AC2         | -         |                                            |

| 0x31   | GSM610            | -         |                                            |

| 0x3b   | ROCKWELL_ADPCM    | -         |                                            |

| 0x3c   | ROCKWELL_DIGITALK | -         |                                            |

| 0x40   | G721_ADPCM        | -         |                                            |

| 0x41   | G728_CELP         | -         |                                            |

| 0x50   | MPEG              | -         |                                            |

| 0x55   | MPEGLAYER3        | +         | For supported MP3 modes, see Chapter 8.2.1 |

| 0x64   | G726_ADPCM        | -         |                                            |

| 0x65   | G722_ADPCM        | -         |                                            |

#### **8.2.4** Supported MIDI Formats

General MIDI and SP-MIDI format 0 files are played. Format 1 and 2 files must be converted to format 0 by the user. The maximum simultaneous polyphony is 40. Actual polyphony depends on the internal clock rate (which is user-selectable), the instruments used, and the possible postprocessing effects enabled, such as bass and treble enhancers. The polyphony restriction algorithm makes use of the SP-MIDI MIP table, if present.

36.86MHz ( $3\times$  input clock) achieves 16-26 simultaneous sustained notes. The instantaneous amount of notes can be larger. 36MHz is a fair compromise between power consumption and quality, but higher clocks can be used to increase the polyphony.

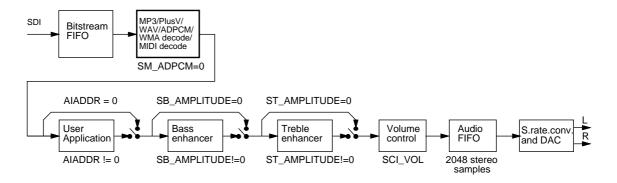

#### 8.3 Data Flow of VS1003

Figure 12: Data Flow of VS1003.

First, depending on the audio data, and provided ADPCM encoding mode is not set, MP3, WMA, PCM WAV, IMA ADPCM WAV, or MIDI data is received and decoded from the SDI bus.

After decoding, if SCI\_AIADDR is non-zero, application code is executed from the address pointed to by that register. For more details, see Application Notes for VS10XX.

Then data may be sent to the Bass and Treble Enhancer depending on the SCLBASS register.

After that the signal is fed to the volume control unit, which also copies the data to the Audio FIFO.

The Audio FIFO holds the data, which is read by the Audio interrupt (Chapter 10.13.1) and fed to the sample rate converter and DACs. The size of the audio FIFO is 2048 stereo ( $2 \times 16$ -bit) samples, or 8 KiB.

The sample rate converter converts all different sample rates to XTALI/256 and feeds the data to the DAC, which in order creates a stereo in-phase analog signal. This signal is then forwarded to the earphone amplifier.

#### 8.4 Serial Data Interface (SDI)

The serial data interface is meant for transferring compressed MP3 or WMA data, WAV PCM and AD-PCM data as well as MIDI data.

Also several different tests may be activated through SDI as described in Chapter 9.

#### 8.5 Serial Control Interface (SCI)

The serial control interface is compatible with the SPI bus specification. Data transfers are always 16 bits. VS1003 is controlled by writing and reading the registers of the interface.

The main controls of the control interface are:

- control of the operation mode, clock, and builtin effects

- access to status information and header data

- access to encoded digital data

- uploading user programs

#### 8.6 SCI Registers

|     |      |          | SCI r                    | egisters, prefix SCI | [_                              |

|-----|------|----------|--------------------------|----------------------|---------------------------------|

| Reg | Type | Reset    | Time <sup>1</sup>        | Abbrev[bits]         | Description                     |

| 0x0 | rw   | 0x800    | 70 CLKI <sup>4</sup>     | MODE                 | Mode control                    |

| 0x1 | rw   | $0x3C^3$ | 40 CLKI                  | STATUS               | Status of VS1003                |

| 0x2 | rw   | 0        | 2100 CLKI                | BASS                 | Built-in bass/treble enhancer   |

| 0x3 | rw   | 0        | 11000 XTALI <sup>5</sup> | CLOCKF               | Clock freq + multiplier         |

| 0x4 | rw   | 0        | 40 CLKI                  | DECODE_TIME          | Decode time in seconds          |

| 0x5 | rw   | 0        | 3200 CLKI                | AUDATA               | Misc. audio data                |

| 0x6 | rw   | 0        | 80 CLKI                  | WRAM                 | RAM write/read                  |

| 0x7 | rw   | 0        | 80 CLKI                  | WRAMADDR             | Base address for RAM write/read |

| 0x8 | r    | 0        | -                        | HDAT0                | Stream header data 0            |

| 0x9 | r    | 0        | -                        | HDAT1                | Stream header data 1            |

| 0xA | rw   | 0        | 3200 CLKI <sup>2</sup>   | AIADDR               | Start address of application    |

| 0xB | rw   | 0        | 2100 CLKI                | VOL                  | Volume control                  |

| 0xC | rw   | 0        | 50 CLKI <sup>2</sup>     | AICTRL0              | Application control register 0  |

| 0xD | rw   | 0        | 50 CLKI <sup>2</sup>     | AICTRL1              | Application control register 1  |

| 0xE | rw   | 0        | 50 CLKI <sup>2</sup>     | AICTRL2              | Application control register 2  |

| 0xF | rw   | 0        | 50 CLKI <sup>2</sup>     | AICTRL3              | Application control register 3  |

<sup>&</sup>lt;sup>1</sup> This is the worst-case time that DREQ stays low after writing to this register. The user may choose to skip the DREQ check for those register writes that take less than 100 clock cycles to execute.

Note that if DREQ is low when an SCI write is done, DREQ also stays low after SCI write processing.

<sup>&</sup>lt;sup>2</sup> In addition, the cycles spent in the user application routine must be counted.

<sup>&</sup>lt;sup>3</sup> Firmware changes the value of this register immediately to 0x38, and in less than 100 ms to 0x30.

<sup>&</sup>lt;sup>4</sup> When mode register write specifies a software reset the worst-case time is 16600 XTALI cycles.

<sup>&</sup>lt;sup>5</sup> Writing to this register may force internal clock to run at  $1.0 \times \text{XTALI}$  for a while. Thus it is not a good idea to send SCI or SDI bits while this register update is in progress.

#### **8.6.1 SCI\_MODE** (RW)

SCI\_MODE is used to control the operation of VS1003 and defaults to 0x0800 (SM\_SDINEW set).

| Bit | Name         | Function                      | Value | Description           |

|-----|--------------|-------------------------------|-------|-----------------------|

| 0   | SM_DIFF      | Differential                  | 0     | normal in-phase audio |

|     |              |                               | 1     | left channel inverted |

| 1   | SM_SETTOZERO | Set to zero                   | 0     | right                 |

|     |              |                               | 1     | wrong                 |

| 2   | SM_RESET     | Soft reset                    | 0     | no reset              |

|     |              |                               | 1     | reset                 |

| 3   | SM_OUTOFWAV  | Jump out of WAV decoding      | 0     | no                    |

|     |              |                               | 1     | yes                   |

| 4   | SM_PDOWN     | Powerdown                     | 0     | power on              |

|     |              |                               | 1     | powerdown             |

| 5   | SM_TESTS     | Allow SDI tests               | 0     | not allowed           |

|     |              |                               | 1     | allowed               |

| 6   | SM_STREAM    | Stream mode                   | 0     | no                    |

|     |              |                               | 1     | yes                   |

| 7   | SM_PLUSV     | MP3+V active                  | 0     | no                    |

|     |              |                               | 1     | yes                   |

| 8   | SM_DACT      | DCLK active edge              | 0     | rising                |

|     |              |                               | 1     | falling               |

| 9   | SM_SDIORD    | SDI bit order                 | 0     | MSb first             |

|     |              |                               | 1     | MSb last              |

| 10  | SM_SDISHARE  | Share SPI chip select         | 0     | no                    |

|     |              |                               | 1     | yes                   |

| 11  | SM_SDINEW    | VS1002 native SPI modes       | 0     | no                    |

|     |              |                               | 1     | yes                   |

| 12  | SM_ADPCM     | ADPCM recording active        | 0     | no                    |

|     |              |                               | 1     | yes                   |

| 13  | SM_ADPCM_HP  | ADPCM high-pass filter active | 0     | no                    |

|     |              |                               | 1     | yes                   |

| 14  | SM_LINE_IN   | ADPCM recording selector      | 0     | microphone            |

|     |              |                               | 1     | line in               |

When SM\_DIFF is set, the player inverts the left channel output. For a stereo input this creates virtual surround, and for a mono input this creates a differential left/right signal.

Software reset is initiated by setting SM\_RESET to 1. This bit is cleared automatically.

If you want to stop decoding a WAV, WMA, or MIDI file in the middle, set SM\_OUTOFWAV, and send data honouring DREQ until SM\_OUTOFWAV is cleared. SCI\_HDAT1 will also be cleared. For WMA and MIDI it is safest to continue sending the stream, send zeroes for WAV.

Bit SM\_PDOWN sets VS1003 into software powerdown mode. Note that software powerdown is not nearly as power efficient as hardware powerdown activated with the XRESET pin.

If SM\_TESTS is set, SDI tests are allowed. For more details on SDI tests, look at Chapter 9.7.

SM\_STREAM activates VS1003's stream mode. In this mode, data should be sent with as even intervals as possible (and preferable with data blocks of less than 512 bytes), and VS1003 makes every attempt to keep its input buffer half full by changing its playback speed upto 5%. For best quality sound, the average speed error should be within 0.5%, the bitrate should not exceed 160 kbit/s and VBR should not be used. For details, see Application Notes for VS10XX. This mode does not work with WMA files.

SM\_PLUSV activates MP3+V decoding. Without this bit set, only MP3 decoding is performed even for files with additional PlusV data.

SM\_DACT defines the active edge of data clock for SDI. When '0', data is read at the rising edge, when '1', data is read at the falling edge.

When SM\_SDIORD is clear, bytes on SDI are sent as a default MSb first. By setting SM\_SDIORD, the user may reverse the bit order for SDI, i.e. bit 0 is received first and bit 7 last. Bytes are, however, still sent in the default order. This register bit has no effect on the SCI bus.

Setting SM\_SDISHARE makes SCI and SDI share the same chip select, as explained in Chapter 7.2, if also SM\_SDINEW is set.

Setting SM\_SDINEW will activate VS1002 native serial modes as described in Chapters 7.2.1 and 7.4.2. Note, that this bit is set as a default when VS1003 is started up.

By activating SM\_ADPCM and SM\_RESET at the same time, the user will activate IMA ADPCM recording mode. More information is available in the Application Notes for VS10XX.

If SM\_ADPCM\_HP is set at the same time as SM\_ADPCM and SM\_RESET, ADPCM mode will start with a high-pass filter. This may help intelligibility of speech when there is lots of background noise. The difference created to the ADPCM encoder frequency response is as shown in Figure 13.

Figure 13: ADPCM Frequency Responses with 8kHz sample rate.

SM\_LINE\_IN is used to select the input for ADPCM recording. If '0', microphone input pins MICP and MICN are used; if '1', LINEIN is used.

#### 8.6.2 SCI\_STATUS (RW)

SCI\_STATUS contains information on the current status of VS1003 and lets the user shutdown the chip without audio glitches.

| Name       | Bits | Description               |

|------------|------|---------------------------|

| SS_VER     | 64   | Version                   |

| SS_APDOWN2 | 3    | Analog driver powerdown   |

| SS_APDOWN1 | 2    | Analog internal powerdown |

| SS_AVOL    | 10   | Analog volume control     |

SS\_VER is 0 for VS1001, 1 for VS1011, 2 for VS1002 and 3 for VS1003.

SS\_APDOWN2 controls analog driver powerdown. Normally this bit is controlled by the system firmware. However, if the user wants to powerdown VS1003 with a minimum power-off transient, turn this bit to 1, then wait for at least a few milliseconds before activating reset.

SS\_APDOWN1 controls internal analog powerdown. This bit is meant to be used by the system firmware only.

SS\_AVOL is the analog volume control: 0 = -0 dB, 1 = -6 dB, 3 = -12 dB. This register is meant to be used automatically by the system firmware only.

#### 8.6.3 **SCI\_BASS** (RW)

| Name         | Bits | Description                                       |

|--------------|------|---------------------------------------------------|

| ST_AMPLITUDE | 1512 | Treble Enhancement in 1.5 dB steps (-87, 0 = off) |

| ST_FREQLIMIT | 118  | Lower limit frequency in 1000 Hz steps (015)      |

| SB_AMPLITUDE | 74   | Bass Enhancement in 1 dB steps $(015, 0 = off)$   |

| SB_FREQLIMIT | 30   | Lower limit frequency in 10 Hz steps (215)        |

The Bass Enhancer VSBE is a powerful bass boosting DSP algorithm, which tries to take the most out of the users earphones without causing clipping.

VSBE is activated when SB\_AMPLITUDE is non-zero. SB\_AMPLITUDE should be set to the user's preferences, and SB\_FREQLIMIT to roughly 1.5 times the lowest frequency the user's audio system can reproduce. For example setting SCI\_BASS to 0x00f6 will have 15 dB enhancement below 60 Hz.

Note: Because VSBE tries to avoid clipping, it gives the best bass boost with dynamical music material, or when the playback volume is not set to maximum. It also does not create bass: there must be bass to enhance in the source material.

Treble Enhancer is activated when ST\_AMPLITUDE is non-zero. For example setting SCI\_BASS to 0x7a00 will have 10.5 dB enhancement above 10 kHz.

Bass Enhancer takes about 3.0 MHz and Treble Enhancer 1.2 MHz at 44100 Hz sample rate. Both can be on simultaneously.

#### 8.6.4 SCI\_CLOCKF (RW)

The operation of SCI\_CLOCKF is different in VS1003 than in VS10x1 and VS1002.

| SCI_CLOCKF bits                         |      |                             |  |  |

|-----------------------------------------|------|-----------------------------|--|--|

| Name Bits Description                   |      |                             |  |  |

| SC_MULT 1513 (                          |      | Clock multiplier            |  |  |

| SC_ADD 1211 Allowed multiplier addition |      | Allowed multiplier addition |  |  |

| SC_FREQ                                 | 10 0 | Clock frequency             |  |  |

SC\_MULT activates the built-in clock multiplier. This will multiply XTALI to create a higher CLKI. The values are as follows:

| SC_MULT | MASK   | CLKI      |

|---------|--------|-----------|

| 0       | 0x0000 | XTALI     |

| 1       | 0x2000 | XTALI×1.5 |

| 2       | 0x4000 | XTALI×2.0 |

| 3       | 0x6000 | XTALI×2.5 |

| 4       | 0x8000 | XTALI×3.0 |

| 5       | 0xa000 | XTALI×3.5 |

| 6       | 0xc000 | XTALI×4.0 |

| 7       | 0xe000 | XTALI×4.5 |

SC\_ADD tells, how much the decoder firmware is allowed to add to the multiplier specified by SC\_MULT if more cycles are temporarily needed to decode a WMA stream. The values are:

| SC_ADD | MASK   | Multiplier addition        |

|--------|--------|----------------------------|

| 0      | 0x0000 | No modification is allowed |

| 1      | 0x0800 | 0.5×                       |

| 2      | 0x1000 | 1.0×                       |

| 3      | 0x1800 | 1.5×                       |

SC\_FREQ is used to tell if the input clock XTALI is running at something else than 12.288 MHz. XTALI is set in 4 kHz steps. The formula for calculating the correct value for this register is  $\frac{XTALI-8000000}{4000}$  (XTALI is in Hz).

Note: because maximum sample rate is  $\frac{XTALI}{256}$ , all sample rates are not available if XTALI < 12.288 MHz.

Note: The default value 0 is assumed to mean XTALI=12.288 MHz.

Note: Automatic clock change can only happen when decoding WMA files. Automatic clock change is done one  $0.5\times$  at a time. This does not cause a drop to  $1.0\times$  clock and you can use the same SCI and SDI clock throughout the WMA file. When decoding ends the default multiplier is restored and can cause  $1.0\times$  clock to be used momentarily.

Example: If SCI\_CLOCKF is 0x5BE8, SC\_MULT = 2, SC\_ADD = 3 and SC\_FREQ = 0x3E8 = 1000. This means that XTALI =  $1000 \times 4000 + 8000000 = 12$  MHz. The clock multiplier is set to  $2.0 \times XTALI = 24$  MHz, and the maximum allowed multiplier that the firmware may automatically choose to use is  $(2.0 + 1.5) \times XTALI = 42$  MHz.

#### 8.6.5 SCI\_DECODE\_TIME (RW)

When decoding correct data, current decoded time is shown in this register in full seconds.

The user may change the value of this register. In that case the new value should be written twice.

SCI\_DECODE\_TIME is reset at every software reset and also when WAV (PCM or IMA ADPCM), WMA, or MIDI decoding starts or ends.

#### 8.6.6 SCI\_AUDATA (RW)

When decoding correct data, the current sample rate and number of channels can be found in bits 15..1 and 0 of SCI\_AUDATA, respectively. Bits 15..1 contain the sample rate divided by two, and bit 0 is 0 for mono data and 1 for stereo. Writing to SCI\_AUDATA will change the sample rate directly.

Example: 44100 Hz stereo data reads as 0xAC45 (44101).

#### 8.6.7 **SCI\_WRAM (RW)**

SCI\_WRAM is used to upload application programs and data to instruction and data RAMs. The start address must be initialized by writing to SCI\_WRAMADDR prior to the first write/read of SCI\_WRAM. As 16 bits of data can be transferred with one SCI\_WRAM write/read, and the instruction word is 32 bits long, two consecutive writes/reads are needed for each instruction word. The byte order is big-endian (i.e. most significant words first). After each full-word write/read, the internal pointer is autoincremented.

#### 8.6.8 SCI\_WRAMADDR (W)

SCI\_WRAMADDR is used to set the program address for following SCI\_WRAM writes/reads.

| SM_WRAMADDR  | Dest. addr.  | Bits/ | Description     |

|--------------|--------------|-------|-----------------|

| StartEnd     | StartEnd     | Word  |                 |

| 0x18000x187F | 0x18000x187F | 16    | X data RAM      |

| 0x58000x587F | 0x18000x187F | 16    | Y data RAM      |

| 0x80300x84FF | 0x00300x04FF | 32    | Instruction RAM |

| 0xC0000xFFFF | 0xC0000xFFFF | 16    | I/O             |

#### 8.6.9 SCI\_HDAT0 and SCI\_HDAT1 (R)

For WAV files, SPI\_HDAT0 and SPI\_HDAT1 read as 0x7761, and 0x7665, respectively.

For WMA files, SCI\_HDAT1 contains 0x574D and SCI\_HDAT0 contains the data speed measured in bytes per second. To get the bit-rate of the file, multiply the value of SCI\_HDAT1 by 8.

for MIDI files, SCI\_HDAT1 contains 0x4D54 and SCI\_HDAT0 contains values according to the following table:

| HDAT0[15:8] | HDAT0[7:0] | Value | Explanation       |

|-------------|------------|-------|-------------------|

| 0           | polyphony  |       | current polyphony |

| 1255        | reserved   |       |                   |

For MP3 files, SCI\_HDAT[0...1] have the following content:

| Bit          | Function    | Value | Explanation        |

|--------------|-------------|-------|--------------------|

| HDAT1[15:5]  | syncword    | 2047  | stream valid       |

| HDAT1[4:3]   | ID          | 3     | ISO 11172-3 1.0    |

|              |             | 2     | MPG 2.0 (1/2-rate) |

|              |             | 1     | MPG 2.5 (1/4-rate) |

|              |             | 0     | MPG 2.5 (1/4-rate) |

| HDAT1[2:1]   | layer       | 3     | I                  |

|              |             | 2     | II                 |

|              |             | 1     | III                |

|              |             | 0     | reserved           |

| HDAT1[0]     | protect bit | 1     | No CRC             |

|              |             | 0     | CRC protected      |

| HDAT0[15:12] | bitrate     |       | ISO 11172-3        |

| HDAT0[11:10] | sample rate | 3     | reserved           |

|              |             | 2     | 32/16/8 kHz        |

|              |             | 1     | 48/24/12 kHz       |

|              |             | 0     | 44/22/11 kHz       |

| HDAT0[9]     | pad bit     | 1     | additional slot    |

|              |             | 0     | normal frame       |

| HDAT0[8]     | private bit |       | not defined        |

| HDAT0[7:6]   | mode        | 3     | mono               |

|              |             | 2     | dual channel       |

|              |             | 1     | joint stereo       |

|              |             | 0     | stereo             |

| HDAT0[5:4]   | extension   |       | ISO 11172-3        |

| HDAT0[3]     | copyright   | 1     | copyrighted        |

|              |             | 0     | free               |

| HDAT0[2]     | original    | 1     | original           |

|              |             | 0     | copy               |

| HDAT0[1:0]   | emphasis    | 3     | CCITT J.17         |

|              |             | 2     | reserved           |

|              |             | 1     | 50/15 microsec     |

|              |             | 0     | none               |

When read, SCI\_HDAT0 and SCI\_HDAT1 contain header information that is extracted from MP3 stream

currently being decoded. After reset both registers are cleared, indicating no data has been found yet.

The "sample rate" field in SCI\_HDAT0 is interpreted according to the following table:

| "sample rate" | ID=3 / Hz | ID=2 / Hz | ID=0,1 / Hz |

|---------------|-----------|-----------|-------------|

| 3             | -         | -         | -           |

| 2             | 32000     | 16000     | 8000        |

| 1             | 48000     | 24000     | 12000       |

| 0             | 44100     | 22050     | 11025       |

The "bitrate" field in HDAT0 is read according to the following table:

| "bitrate" | ID=3 / kbit/s | ID=0,1,2 / kbit/s |

|-----------|---------------|-------------------|

| 15        | forbidden     | forbidden         |

| 14        | 320           | 160               |

| 13        | 256           | 144               |

| 12        | 224           | 128               |

| 11        | 192           | 112               |

| 10        | 160           | 96                |

| 9         | 128           | 80                |

| 8         | 112           | 64                |

| 7         | 96            | 56                |

| 6         | 80            | 48                |

| 5         | 64            | 40                |

| 4         | 56            | 32                |

| 3         | 48            | 24                |

| 2         | 40            | 16                |

| 1         | 32            | 8                 |

| 0         | -             | -                 |

#### **8.6.10** SCI\_AIADDR (RW)

SCI\_AIADDR indicates the start address of the application code written earlier with SCI\_WRAMADDR and SCI\_WRAM registers. If no application code is used, this register should not be initialized, or it should be initialized to zero. For more details, see Application Notes for VS10XX.

#### 8.6.11 SCI\_VOL (RW)