### MASTERING FPGA EMBEDDED SYSTEMS

A Case Study Approach to Designing and Implementing FPGA-Based Embedded Systems with TFT LCDs

#### MASTERING FPGA EMBEDDED SYSTEMS

A Case Study Approach to Designing and Implementing FPGA-Based Embedded Systems with TFT LCDs

By

Aharen-san

TABLE OF CONTENTS EDA TOOLS WHAT'S EDA **EXAMPLES OF EDA TOOLS** TYPICAL FEATURES OF EDA TOOLS **SIMULATION** PCB DESIGN SOFTWARE DEVELOPMENT EDA TOOLS FOR FPGA DEVELOPMENT THE USUAL USER STEPS CREATE A PROJECT WRITE YOUR CODE **PIN ASSIGNMENT** THE USUAL COMPILER STEPS TIMING ANALYSIS **GENERATING A PROGRAMMING FILE** DOWNLOADING YOUR DESIGN INTO AN FPGA QUARTUS PRIME, BY INTEL ABOUT QUARTUS AND INTEL SETUP DOWNLOADING QUARTUS SETUP INSTALLING QUARTUS WHERE EVERYTHING IS - PROJECT NAVIGATOR

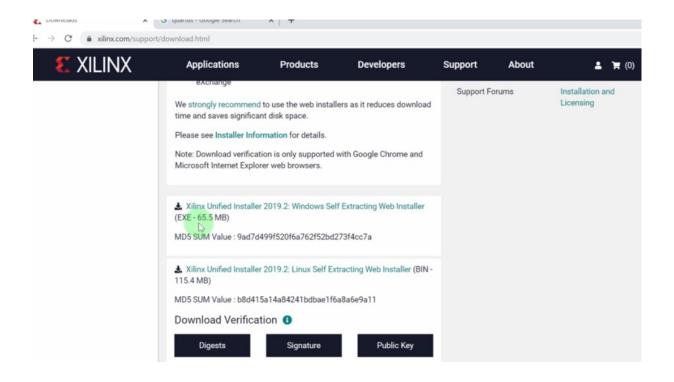

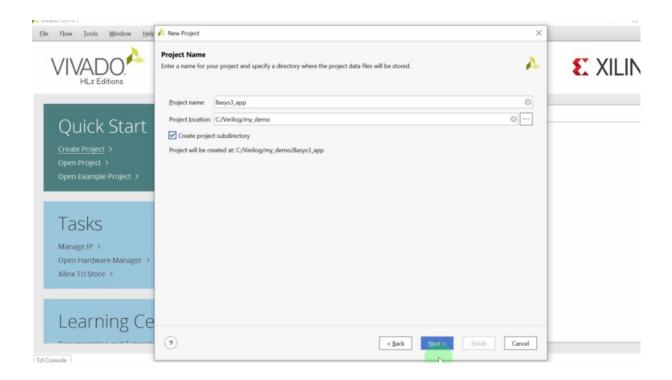

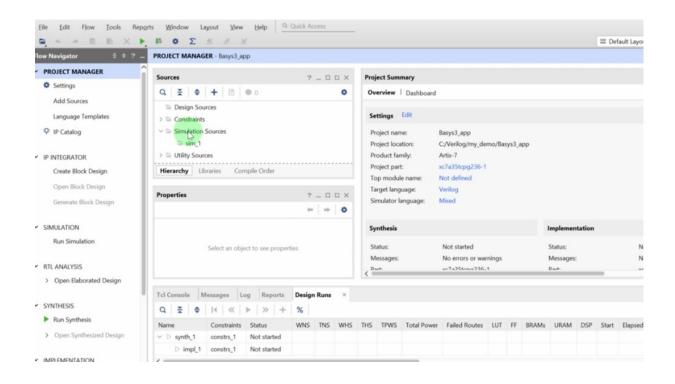

WHERE EVERYTHING IS – TASKS WHERE EVERYTHING IS - IP CATALOG SETUP FOR IMPLEMENTATION HELLO WORLD - CREATE A PROJECT **HELLO WORLD - TOP MODULE SOURCE FILE HELLO WORLD – IMPLEMENTATION** HELLO WORLD - PROGRAMMING THE FPGA EDA PLAYGROUND, BY DOULOS ABOUT EDA PLAYGROUND AND DOULOS EDA PLAYGROUND SETUP WALKTHROUGH CODE ENTRY WALKTHROUGH LEFT TOOLBAR Walkthrough Other Tools DEMO CODE EXAMPLE **DEMO SIMULATION DUMP SYSTEM TASKS DEMO SIMULATION CONTROL SYSTEM TASKS** VIVADO DESIGN SUITE. BY XILINX ABOUT VIVADO DESIGN SUITE AND XILINX SETUP DOWNLOADING VIVADO SETUP THE VIVADO INSTALLATION WIZARD **CREATING A PROJECT** WALKTHROUGH PROJECT MANAGER WALKTHROUGH IP CATALOG

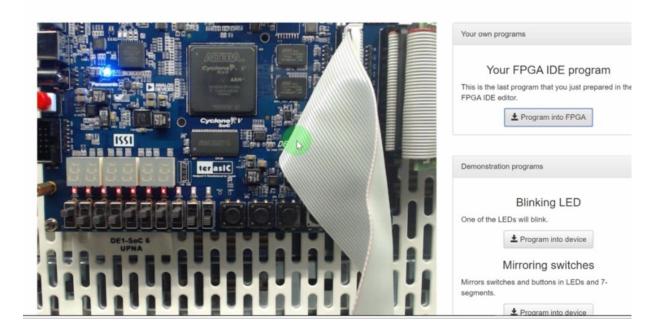

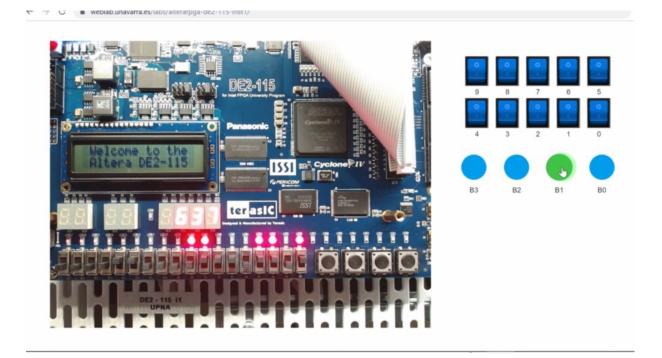

WALKTHROUGH SOURCE FILES WALKTHROUGH CONSOLE OUTPUT AND **MESSAGES** WALKTHROUGH SIMULATION WALKTHROUGH PIN ASSIGNMENT WALKTHROUGH TOP MODULE CODE WALKTHROUGH BITSTREAM FILE GENERATION WALKTHROUGH THE HARDWARE MANAGER LABSLAND ABOUT LABSLAND WALKTHROUGH FPGA LAB VERILOG IDE DEMO PIN ASSIGNMENT VERILOG IDE DEMO ADDER CODE VERILOG IDE DEMO ADDER LIVE DEMO VERILOG IDE DEMO MULTIPLIER LIVE DEMO RECOMPILING UPLOADING DEMOS MOTIVATION HARDWARE DESIGN MOTIVATION SOFT PROCESSORS **INTRO TO FPGAS FPGA OVERVIEW FPGAS VS ASIC**

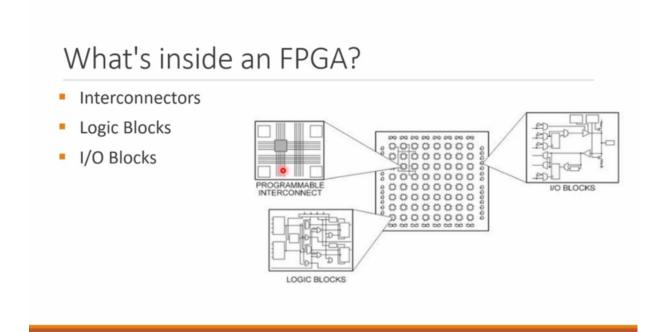

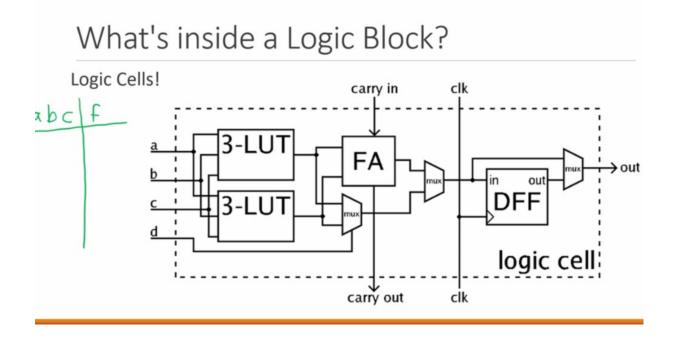

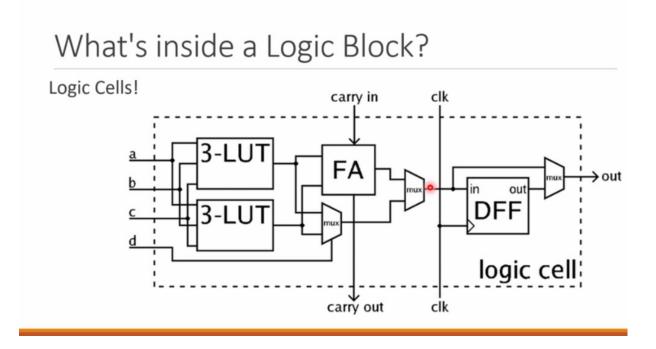

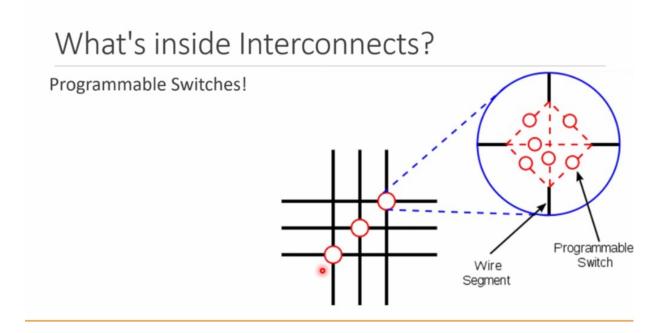

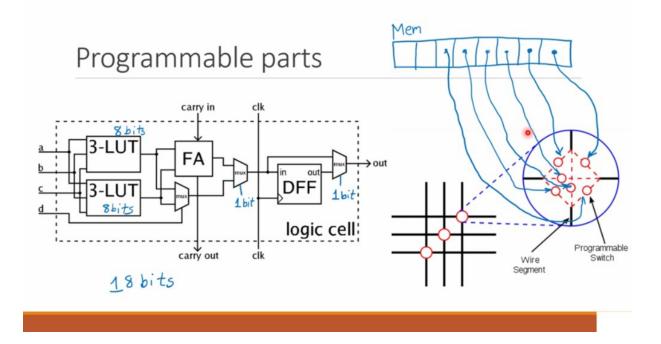

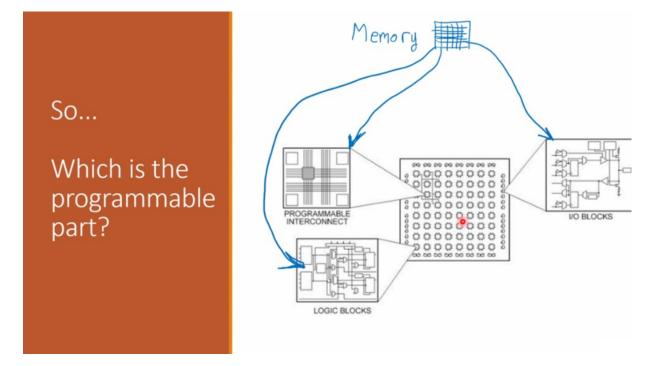

WHAT'S INSIDE AN FPGA WHAT'S INSIDE LOGIC BLOCKS ADDERS AND **FLIP FLOPS** WHAT'S INSIDE INTERCONNECTS WHAT'S INSIDE I O BLOCKS WHICH IS THE PROGRAMMABLE FPGAS VS CPLDS HOW IS AN FPGA PROGRAMMED WHO MAKES FPGAS WHAT HARDWARE CAN BE IMPLEMENTED WITH AN FPGA WHERE TO GET A BOARD **BOARD UNBOXING** THE DE0-CV BOARD WEBSITE DE0-CV BOARD CD CONTENT SKIMMING THROUGH THE MANUAL THE FPGA DEVELOPMENT PROCESS THE STEPS YOU NEED TO TAKE CREATE A PROJECT WRITE YOUR CODE **ASSIGN PINS** PIN ASSIGNMENT DEMO SPECIFY TIMING CONSTRAINTS

PROPAGATION DELAYS EXAMPLE TIMING IN SEQUENTIAL SYSTEMS WHY THIS MATTERS IN FPGAS WHERE THE COMPILER TAKES ON TIMING ANALYSIS **PROGRAMMING FILES INSTALLING QUARTUS PRIME** SHOWING YOU AROUND QUARTUS PRIME LOOKING AT THE TOP-LEVEL TEMPLATE CODE ENTERING SOME PROOF-OF-CONCEPT CODE COMPILING YOUR DESIGN **PROGRAMMING YOUR DEVICE - JTAG MODE PROGRAMMING YOUR DEVICE - ACTIVE SERIAL** MODE GETTING IT BACK TO ITS FACTORY STATE SYSTEM BUILDER THE EASIEST WAY TO JUMPSTART YOU APPLICATIONS SYSTEM DESCRIPTION LOOKING AT THE ADDER CODE LOOKING AT THE BLINKY CODE LOOKING AT THE INSTANTIATED MODULES CODE **PROGRAMMING THE ADDER INTO THE BOARD**

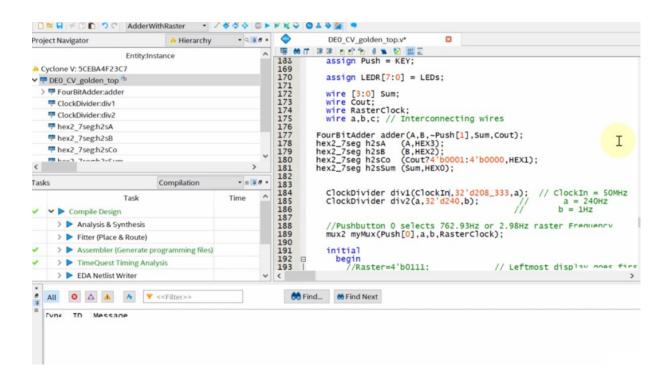

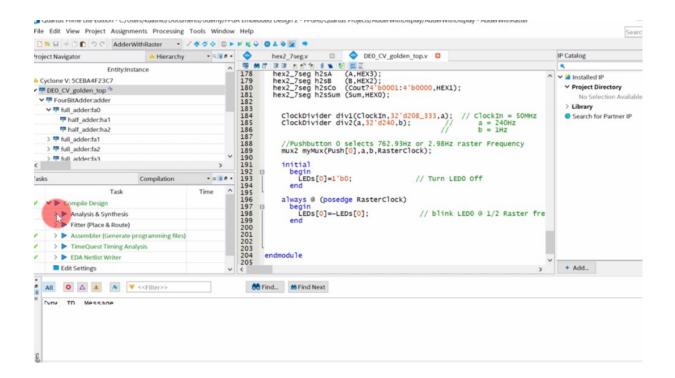

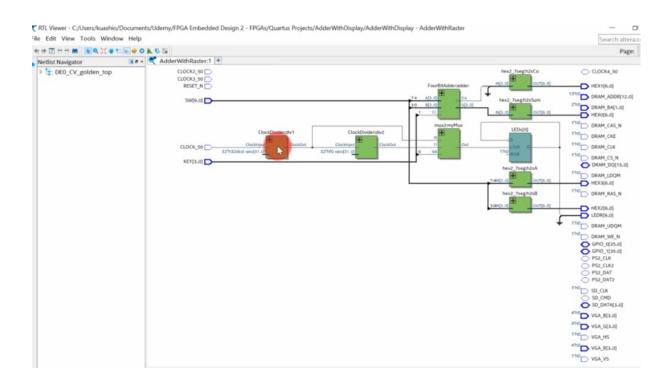

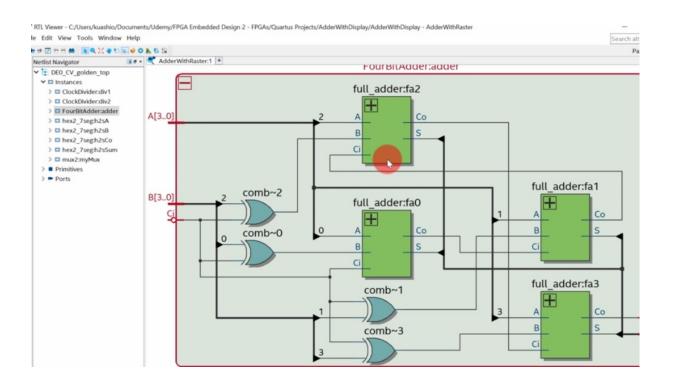

SCHEMATIC RTL DEMO

#### EDA TOOLS

First let me tell you about EDTA tools so in this project we'll get to know what the tools are.

#### In this lesson: EDA Tools

- What's EDA?

- Examples of EDA Tools

- Features of EDA Tools

We'll see some examples of EDTA tools that are available out there and we'll get to know the typical features of EDA tools. So let's get started.

#### WHAT'S EDA

First what exactly is EDTA. Well the A stands for electronic design automation and that's what it means. It means automating the design process of any electronic devices by electronic we mean hardware usually. But it also supports software so these are software suites for creating hardware. That's a nice definition of PDA. They are similar to IV's which are integrated development environment for creating software. So you may think of Cold Warrior or Eclipse or Visual Studio.

#### What exactly is EDA?

- Electronic Design Automation.

- Software Suites for creating Hardware.

- Similar to IDEs.

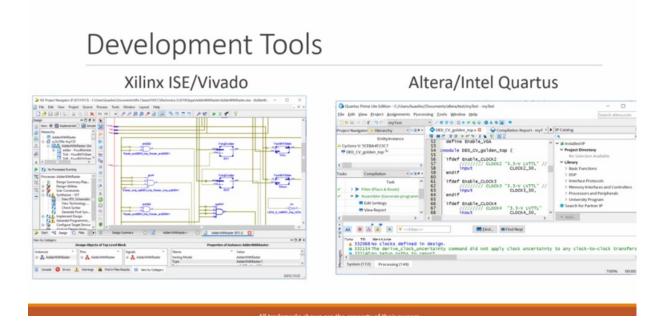

These are integrated development environments but either way tools are something else but they are similar to ideas in that they have several modules that you can work with and you can make different projects with different objectives. So you are not completely expected to know how to use the whole suite but rather just the parts that apply to your design. Of course you learn as you get more and more experience so here we have an illustration of the value Design Suite which is one of the tools you'll see in this project. And this is an FPGA designed too. There's a distinction between traditional IDEO tools and just FPGA tools.

#### EXAMPLES OF EDA TOOLS

So here we have some examples of EDTA tools we have out young designer which specializes in hardware simulation and printed circuit board design. We have Eagle which also has a simulator but these two are mainly for designing BCBS.

## Examples of EDA Tools Altium Designer EAGLE Vivado Quartus Multisim/Ultiboard Fritzing KiCad

We have the father Design Suite which is for FPGA. We have courts we have multi Sim an ulti board which are National Instruments tools for simulation and PCV design respectively there's a nice tool called fitting which is a simulator for creating both picked a graphical diagrams in a bread board and simulation Jacob is a very popular open source tool for PCV design.

#### TYPICAL FEATURES OF EDA TOOLS

So let's talk about the typical features of PDA tools. First we have schematic capture. This is where you enter a schematic diagram which is a graphical interface. We have HDL code entry with a text editor to enter very low or V HDL code.

#### Features of EDA Tools

- Schematic Capture.

- HDL Code Entry.

- Simulation.

- FPGA Design.

- Software Development.

Most of these tools have a simulator either analog or digital or mixed mode of course we also have FPGA design. This is the part we are interested in. We have software development and PCV design.

#### SIMULATION

So let me quickly summarize what simulation is in an easy way to. It means gathering data from the circuit models you are using in your design so that you can predict how the physical circuit would behave. Now there are several levels of simulation you can run so a simulation has the following elements.

#### Simulation

Gathering data from the circuit models in the design.

Typical elements:

- Digital Simulation

- Analog Simulation

- Mixed Mode Simulation

- Microcontroller & FPGA Simulation

We have digital simulation which deals with zeros ones high impedance and unknown states but that's it. It doesn't deal with voltages and currents. If you need those we have analog simulation which can simulate an amplifier for example or a low pass filter and finally we have mixed mode simulation. Let's say you have some logic gates in your design and you have some up amps and you want to see how it would behave in the real world. You can run a mixed mode simulation which is actually the same analog simulation with analog models for the digital elements.

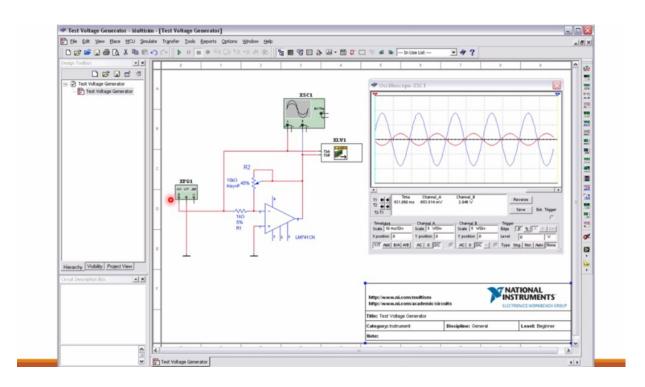

There is also microcontroller and FPGA simulation in case your idea too supports microcontrollers. It could have a simulator that works just as the microcontroller would work with your code so it requires a compiler tool usually. And as for FPGA simulation what we get is a simulator for the digital part. So I guess that would be the same digital simulation we just saw so here we have a nice simulation in multi Sim. This is National Instruments simulator and as you can see here we have an inverting amplifier with a part on the feedback resistor so we can change the game. We have an oscilloscope at the output right here so we can see the signals and it's connected to both the input and the output in its two channels. So here's the result. And while the input comes from a function generator. So this is a nice example of a very popular analog simulator.

#### PCB DESIGN

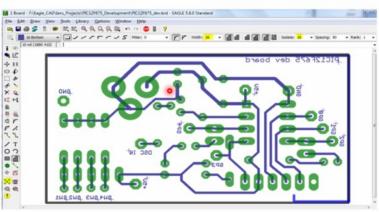

PCV design is another feature of EDA tools which is very popular. Actually there are some tools that are only used for PCV design by their users and sadly most of these tools are underutilized because again people use them only to design pieces when they have a lot of other features. But anyway for PCV design what we need is routing of copper layers so remember a PCV has a lot of conductors which are printed on the board and these are layers of copper and the routing of copper layers is a very hard to solve computational problem. If you know about computational complexity you'll know about and beat problems. So this is an empty heart problem which is as hard as the hardest computational problem out there. And I'm mentioning this because this consumes a lot from your computer.

#### PCB Design

- Routing of Copper Layers

- SilkScreen Layers

- SolderMask

- Drilling

- Design Rules Check

If your PCV tool contains an outdoor router and I'm talking about a good auto router we also designed the silk screen layers which are the layers that have text or logos on them. These are usually white and this one for example says the number of the board right here. It says pick some number Development Board and notice that the text is flipped. That means that this text has to be printed on the other side of this board. We also designed the Sadr mask which are the parts that are shown here in green. So these are the pads where Sadr would go and BCBS usually have a coating of some material very similar to nail polish which prevents Sadr from sticking into the tracks and only allows you to Sadr where you are supposed to Sadr. So these green parts are where the Sadr mask would not go. So the Sadr mask is the coating. And again this layer should be a negative layer which makes rings around these green pads where the coating is not supposed to go. We have drilling files that tells a drilling machine where to punch holes. So all of these pads are supposed to have drilling on them because this is a through hole PCV not a surface mount PCV and finally PCV designed tools also offer design rules check. So there are some guidelines provided by the manufacturers of BCBS because you are going to send your design to some factory to be built. Usually in high quantities and so these machines have some guidelines some requirements for example the clearance you need between elements and the clearance you need between the tracks and the borders. All of these rules are checked by the software in order to comply with the requirements of the manufacturing machines. You are going to use. You may build your own boards either manually or with some machine and even then these rules are useful

#### SOFTWARE DEVELOPMENT

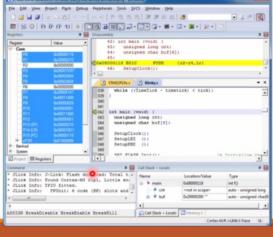

As for software development this is included in 88 tools mainly because of the microcontrollers or the soft processors. Your design may contain some elements of software development tools are actually the same ones found in 80s. So we have a text editor with usually syntax highlight to create your code and show it to you later. We have a compiler assembler a linker the works a compiler tool chain we usually have a D assembler so that you can see that this assembly as seen in this picture right here where you can see how your source code resulted in assembly code.

#### Software Development

Many EDA tools have software dev tools for the microcontrollers or soft processors in the design.

Typical Elements:

- Text Editor with syntax highlight

- Compiler/Assembler/Linker

- Disassembler

- Debugger

We also have a debugger and in this picture we have Kyle tools showing exactly that the debugger. So here are the registers of an arm cortex CPA. Here's the source code and here's the disassembled code. Here we have some variables that can be shown to you in runtime. And this debugger usually contains a simulator so you can simulate whatever you're designing or you may download your design to an actual microcontroller. And from the microcontroller report back to the I.D. to show you the same debugger but with real data in these registers or memory location watches.

#### EDA TOOLS FOR FPGA DEVELOPMENT

Now what we are most interested in are LDA tools for FPGA development so in this project we'll talk about just that idea. Tools for FPGA ace. We'll talk about the usual user steps the steps you need to take in order to create your FPGA applications.

#### In this lesson: EDA for FPGAs

- The Usual User Steps

- The Usual Compiler Steps

We'll talk about the usual compiler steps which are the steps taken by the software and that's it. Now I want to make a little disclaimer please bear with me in this project because it contains a lot of the elements we already saw in the previous projects and I think that it's not only important that you keep all of this in mind but I will also mention some new important details so let's get started.

#### THE USUAL USER STEPS

Here are the usual user steps the steps you need to take to create your FPGA designs. So first you create a project. Then you write your code and then you usually simulate and there's a loop here. An explicit loop I have created here so that you can simulate and when you find out that your circuit is not behaving as you want it then you rewrite your code or modify your code rather simulate again modify your code.

And when you're happy with your design you can go ahead to the next step. So the next step would be the implementation if you want to get your design into NAFTA. Then you have to assign the pins in the FPGA package then specified timing constraints which are your timing requirements. The most basic of these is the clock frequency. You want to support. Then you compile which is what the computer does on its own. And finally you can download your design into your hardware that is your FPGA or most likely your development board. Now let me quickly tell you some details about all of these steps.

#### CREATE A PROJECT

The first step is to create a project so ideal tools usually work with projects. And so you have to provide some information for the tools to know how to create your application. So first we have the purpose. You may simply want to simulate your design or you may be interested in getting it on an FPGA. So as we just saw simulation requires about three steps. But FPGA design requires many more if you want to design for a target FPGA.

#### Create a Project

- EDA tools usually work with projects.

- Information you provide:

- Purpose (Simulation or FPGA)

- Target FPGA

- Target Board (If supported)

- Primary Source Language/Method

- Source and Libraries (IP Cores)

You have to specify which chip you are using the target board if your tool supports several implementations of the same FPGA on different boards. Well you get to specify it. Now this is usually kind of optional but you get sometimes to specify which is the language you intend to use for code entry. Very logger v HDL but most tools are

bilingual and you usually get to select which IP project that's third party source or libraries that you get to include in your project.

#### WRITE YOUR CODE

The next step is writing your code and once more. Most idea tools support very low end VH deal some tools support schematics but these schematics aren't really for writing your code. These are usually for showing you the net list created by the Synthesis tool. By that I mean what your tool interpreted what it understood from your source code in very low or VH deal. So these schematics are for you to validate that the tool got it. The tool understood what you intended to create. There are two types of schematics shown for example in the other.

#### Write your Code

- Most EDA tools support:

- Verilog

- VHDL

- Schematics (RTL and Technology)

- You have to include all modules in your project.

- Lots of IP-Cores available.

We have RTL schematics and technology schematics. The RTL schematic is a logical schematic which may show you gates and multiplexes and flip flops or even decoders whereas the technology schematic is limited to the technology available inside the Target

FPGA chip. So let's say your FPGA contains Gates. Then the RTL schematic will show you those gates and the technology schematic will also show you those gates. But on the other hand if you're FPGA as most FPGA does not contain free gates for you to use but rather lookup tables then the technology's schematic will show you. Lookup tables and going back to writing your code you have to include all modules you are going to use in your project. This is just the same as with software development but you don't have to write the source for all of the modules you're going to include. You can use IP project that are available from the vendors and many of those IP project are available for free.

#### **PIN ASSIGNMENT**

When it comes to assigning pens the EPA tools that support implementation usually allow you to enter some important information about these paints so you get to specify the location of the pins that is which physical pin in the FPGA chip goes to which input output bought off your top level module.

#### Assign Pins

- Some important information about pins is necessary:

- Pin Location

- Pin Direction

- Schmitt Trigger

- Pull Resistors

- Slew Rate

- Many, many more!

- This info resides ultimately in some text files.

You can indicate the direction of the pin either it's an input pin an output then or a bi directional pin your inputs may be Schmidt trigger they may have pulled resistors either pull up or pull down resistors you may specify even analog details about them for example slow rate and there are many many more aspects you may specify of Europeans all of this may vary from idea a tool to EDI to but this information usually is stored in some text file that you may modify.

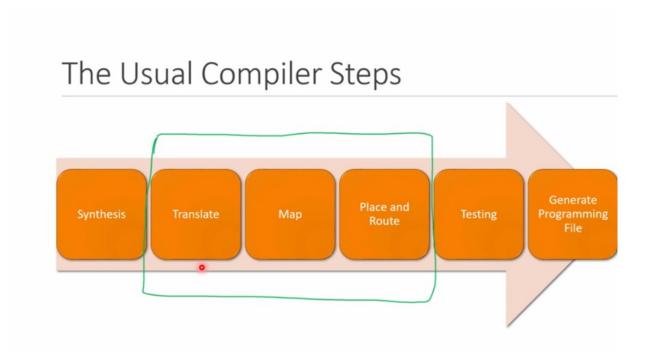

#### THE USUAL COMPILER STEPS

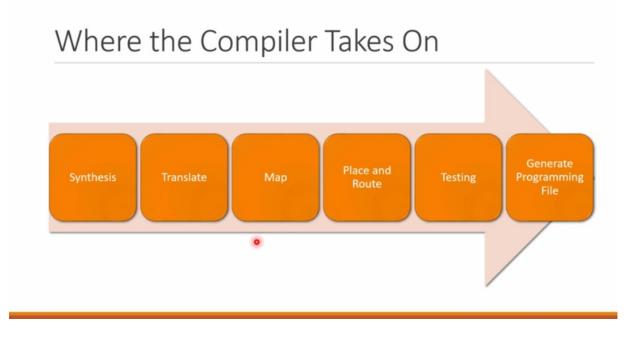

No the compiler steps are synthesis. Translate map place route testing and generating a programming file. These are the steps shown in the site links tool chain. That is the one used by the vato Design Suite and their names may vary from tool to tool. Actually these may have different names in quotes for example so synthesis means converting your RTL design into a net list representation.

Like I said this means what the compiler understood from your very logger VH DL source code implementation means three steps translate map place and root. So going back to the flow diagram we can see these steps which are shown right here. Translate map place and route. So once again these three steps are what's usually known as implementation. This is what the compiler does to create your design for an FPGA. The difference is that synthesis is performed for both implementation and for simulation. So when you simulate the compiler has to understand what you mean with your code. So synthesis is always performed and then the implementation has these three levels once again these three steps are named differently between platforms. So roughly translate means getting the net list into some code that the FPGA can create.

So the translation may produce an intermediate representation of your hardware then map consists on assigning the intermediate elements to the available elements in your FPGA and finally placing root means selecting which elements which were mapped are going to go where in your FPGA and routing between these elements to create the already mapped design. You don't have to do anything about these steps and they may output some errors or warnings which you may have to correct in your code but this is all the responsibility of the compiler. You simply have to sit back let it work and see if the output prompts you to do some changes.

#### TIMING ANALYSIS

There's a timing analysis that the tools often enabled you to perform and this is to test the implementation you just made.

#### Timing Analysis

- The implementation steps take timing constraints as rules

- The generated circuitry is analyzed for compliance with constraints

So when your design was implemented these implementation steps will have taken into account the timing constraints you must have entered and these timing constraints are considered rules for the implementation. So the generated circuitry is then analyzed by the tool to verify that it compliance with all of these constraints.

#### GENERATING A PROGRAMMING FILE

One of the final steps is generating a programming file. Intel calls this assembly code but it's not the typical assembly code in microprocessors sailing schools it bit stream which is I think a better name. This is only a binary file. This file may go to the FPGA which usually has a RAM memory to store this design.

#### Generating a Programming File

- Intel calls it "Assembly".

- Xilinx calls it "Bitstream".

- This is the binary output.

- Goes to the FPGA, or On-Board Flash.

You know what that means. That means that when you turn off the power then the design is lost. So it may also go to a onboard flash and FPGA are usually designed that way. The chip has a RAM memory to store the design in the FBI and it's usually required to have a supporting flash memory onboard to dump that design into the FPGA on startup so let me tell you a bit more about this last point.

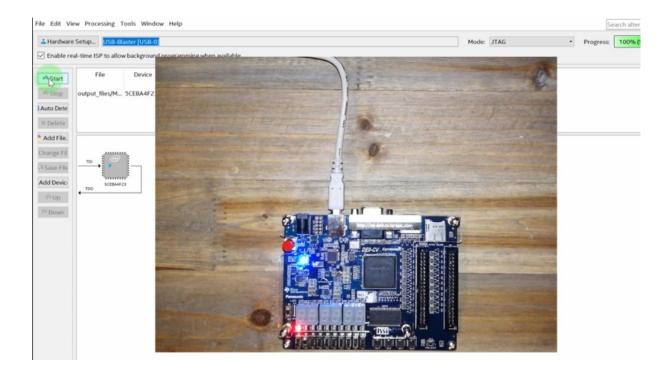

#### DOWNLOADING YOUR DESIGN INTO AN FPGA

Downloading your design into the FPGA means that it goes to a RAM memory because most FPGA A's have a RAM memory where they store your design. You know what that means don't you. That means that this is volatile. So when you turn off the power the design is lost. Does that make sense. Well it makes sense in that Ram memories very fast to use and to program so downloading to the FPGA directly is convenient for development because when you are developing your application it will load faster and you're usually not interested in keeping that design in your FPGA anyway.

#### Downloading your Design

INTO THE FPGA

- o Usually in RAM.

- o This is Volatile!

- o Convenient for development.

INTO A NON-VOLATILE MEMORY

- o Downloaded at power-on.

- This is part of the boot-up procedure.

- o Convenient for deployment.

Now when you download your design into a non-volatile memory that's usually on the same board as the FBA. Well that gets

downloaded into the FPGA at power on notice that when you program this memory it will take longer than when you programmed the RAM memory so that's not so convenient for development and this download process that goes on from the RAM memory into the RAM memory that's into the FPGA. This is all part of the boot up sequence of the FPGA. So any applications you know like your TV or your smartphone or whatever electronics you have that contains an FPGA if that FPGA implements his memory in RAM it must have some non-volatile memory onboard that as part of the boot up procedure dumps this design from non-volatile memory to Ram and finally. Well this is convenient for deployment when you want to ship your designs you programmed the flash memory so that every time the user turns on the device your design will be loaded into the FPGA at power on.

#### QUARTUS PRIME, BY INTEL

Now it's time to talk about quietest prime so let's see what we'll talk about in this project. First I'll tell you about Clark toast prime and intel. I'll tell you about the setup that's required to install and get your environment up and running.

#### In this lesson: Quartus Prime

- About Quartus Prime and Intel

- Setup

- A Quick Walkthrough

- Code Example

- Simulation

- Implementation

I'll give you a quick walkthrough of this PDA too. I'll show you a code example then a simulation. And finally an implementation. That's because I will show you all of the steps that are supported by this very powerful tool. So let's get started.

#### ABOUT QUARTUS AND INTEL

So let me tell you about Curtis and Intel. CURTIS Prime is a fullfledged FPGA development tool. By that I mean that it supports all of the steps we have just mentioned for FPGA development. So this includes simulation and implementation. You may remember that this LDA tool is featured in our second project. The basic FPGA training so you may have some practice on this tool. But anyway I hope you learn some new tricks as you see the examples I'm about to show you now.

# About Quartus Prime and Intel Quartus Prime is a full-fledged FPGA development tool. Featured in our second course: Basic FPGA Training. It offers free licenses. Setup starts at download. Made by Intel, who acquired Altera.

Although Quark This is a commercial application Intel offers some free versions and licenses that are free of cost and these usually have some classes that require you not to charge for your designs and these are also limited in this size of the target application. But these licenses work pretty well for development boards for hobbyists and definitely for discourse. Now the setup starts at download. You get to download several modules into your installation of quarters and Intel makes it easy for you to choose which elements you want to include in order to make both your download later and your installation process faster needless to say. This is an Intel product but you may also know that until recently acquired Altera which was the original company that developed both Quark Does Prime and the manufacturer of all Altera FPGA. So if you were familiar with ultra well now it's Intel. It's been some years now since the acquisition but you may still see the Altair a name out there in some FPGA is.

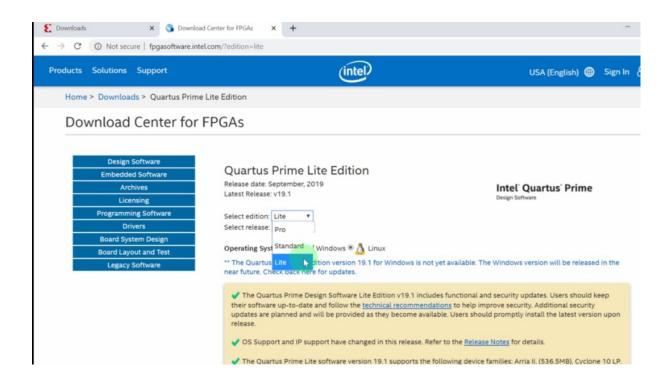

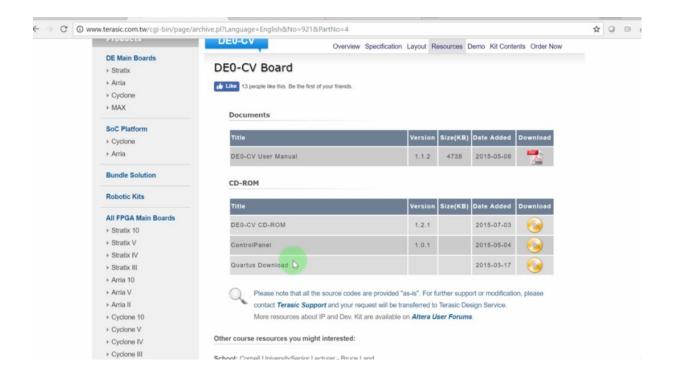

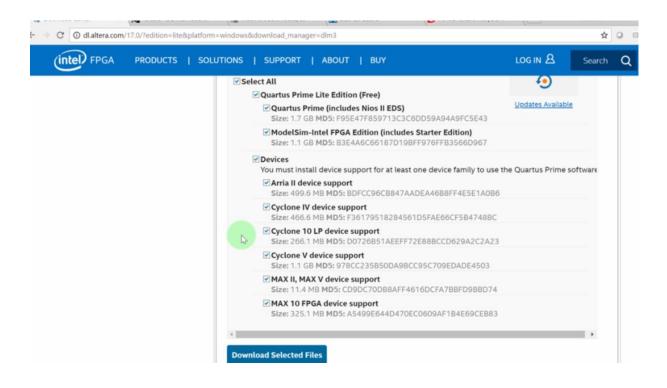

# SETUP\_ DOWNLOADING QUARTUS

So the first step in using cordless prime of course is downloading it and so you can make a web search. Here I have a Google search for cactus. It's not a very common name. So the first result is FPGA design software. Intel called the spring. Just make sure you go to Intel's Web site. So this is the core. This Web site if you scroll down I'm sure you can find the download space which is here features and download and we have several versions. So we have the prime pro edition the prime standard edition and the prime Late Edition. This is the one you want if you want it for free. So this is the download page and I think it requires some explanation.

So first you get to decide which edition you want. We have the pro the standard and the light editions. Once again we want the light edition and you get to select the version the release. So as you can see we get from nineteen point one which is the latest all the way down to version 3. So as always I recommend the latest version. But there's a little problem with this one and that's if you are using windows you can't select windows for this one because as this note says it's not ready yet since I'll be working with Windows.

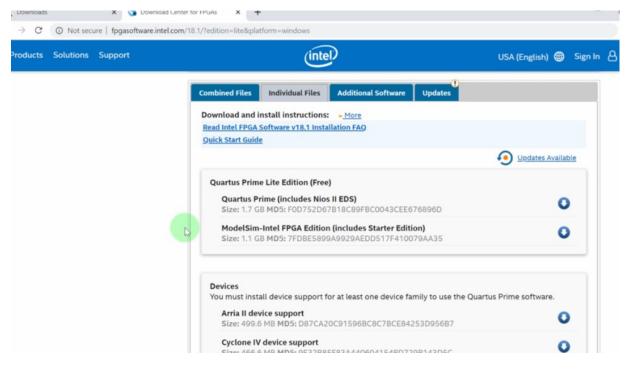

I'll work with the earlier version if you're working with Linux and you want to use release nineteen point one You are free to do so. But I will select eighteen point one as you can see now I can select windows and scrolling down you will see all of the elements you can download. So right here you get to decide if you want to download all of the files combined into one single download which is not usually recommended because of the size of the download. This is five point eight gigabytes. And the default is individual files in this tab right here. And you'll notice that there are several separate elements. It's not that complicated. You just have to download the executable files

you want. In my case I will download quite as subprime which is the FDA too.

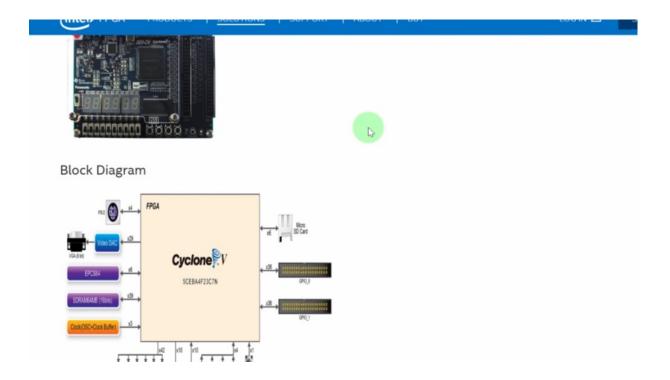

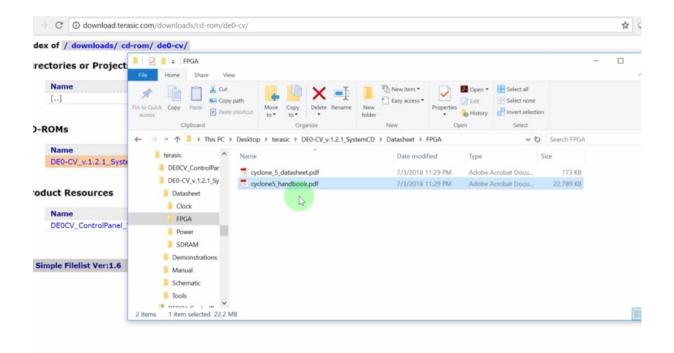

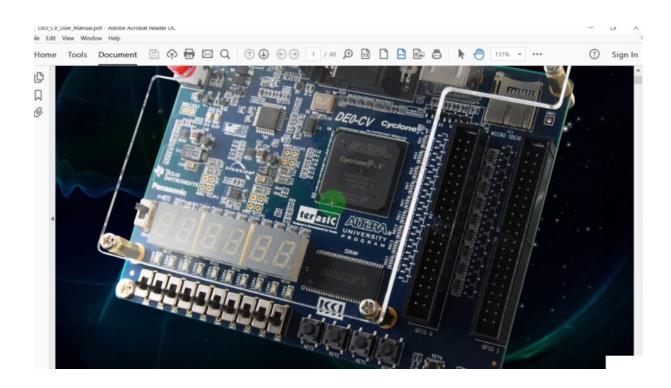

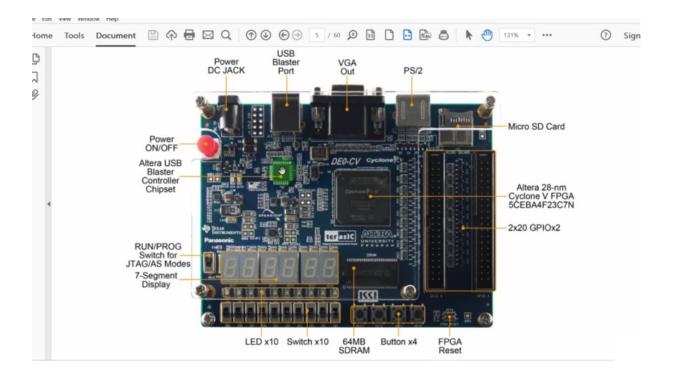

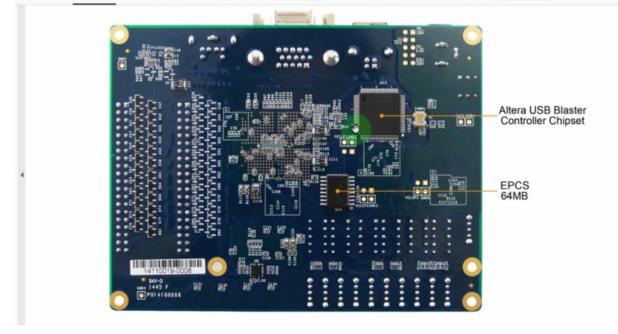

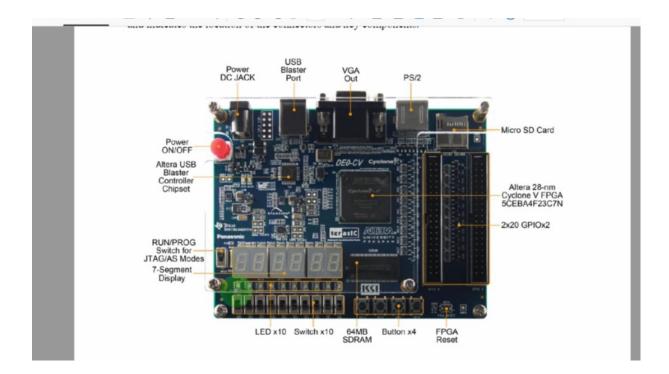

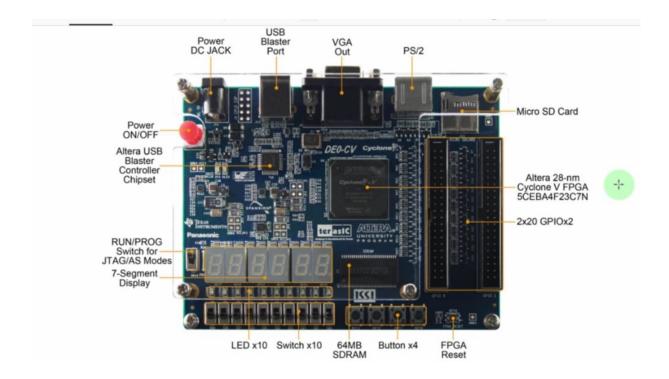

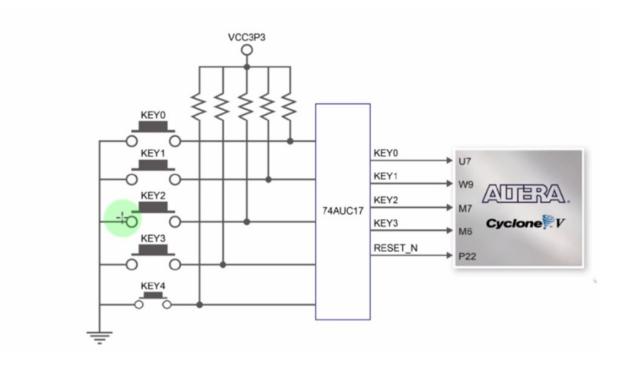

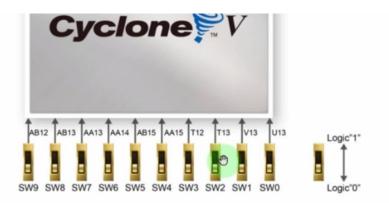

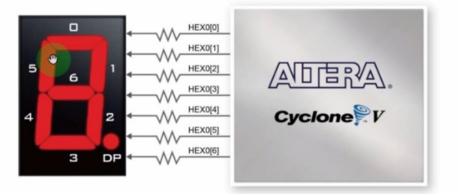

And I will download model Sim which includes the FPGA edition and the Starter Edition. One of these two is the one you are interested in and finally you get to decide which devices you want your installation of characters to support. So Altera or now Intel has several families of FPGA. One is called Aria. There's the cyclone family with several versions. The max family. So since I will be using the DS Development Board let me show you. This is the board I'll be using. This is the D 0 CV board where CV stands for cyclone 5. Then I want to support the cyclone 5 FPGA base and I'm sure you can distinguish a cyclone right here which is the logo for the cyclone five FPGA is so this board has a bunch of IO some switches some LCD some segment displays buttons and a connector with access to virtually every pin in the FPGA. So going back I will select cyclone five device support if you have any other development board and you know the FPGA it has on it then you should select to download support for that FPGA as well.

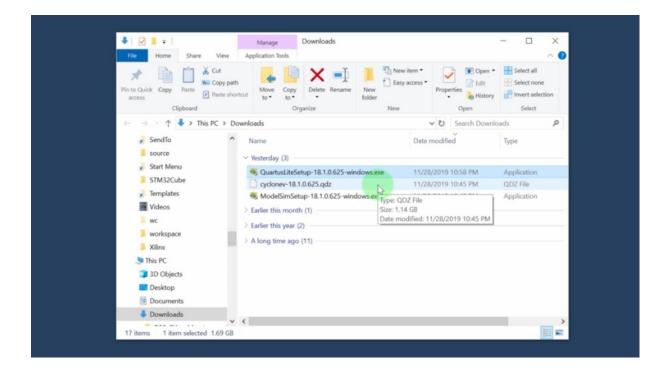

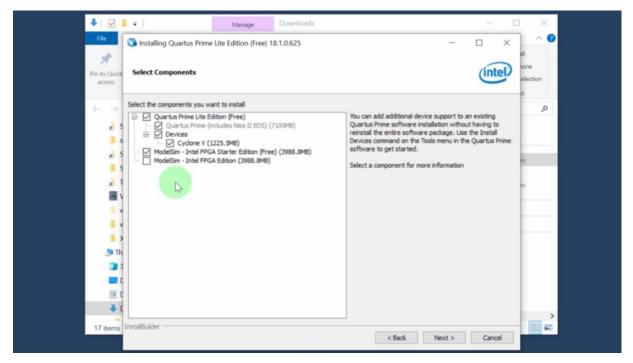

# SETUP\_INSTALLING QUARTUS

So here we have what I've downloaded. Here's the installer for Courtis. Here's the support package for the cyclone five FPGA and this is the model Sim installer. Now the quietest does installer is smart in that it will check in the same directory for the other installers.

You may have downloaded and it will offer you to install them along with quarters. So let's don't click on the quietest light setup so first. Just make sure that you're installing the free edition. That's the LATE EDITION. Next we have to agree to the terms you get to choose the directory where you'll install and this is the part I told you about where you get to choose which elements to install. Now the elements that appear here are based on the other installers you've downloaded for example here we have the quotes to subprime Late Edition installer but then we have devices here and only one is shown which is the cyclone 5 and that's the download. I have along with Curtis right here.

Notice that I have models him also in this directory so model same is shown here. Now the default is to install the Starter edition of model Sim which is set to be free and we also get to install another edition that doesn't see starter just until FPGA edition. So it seems this is all we need and we are okay with these default settings so we are okay to go to the next step which is a summary and we get to install now. And as you know this may take a while once it's done you get the usual stuff among which we have to launch the USP blaster to driver installation. So this is a device driver for the hardware downloader into many of Intel's boards. So you want to do this and here you just have to follow along finally you get to choose the license if you want to buy a license or just run Cordis. Remember that this is a late edition so you get to run it for free.

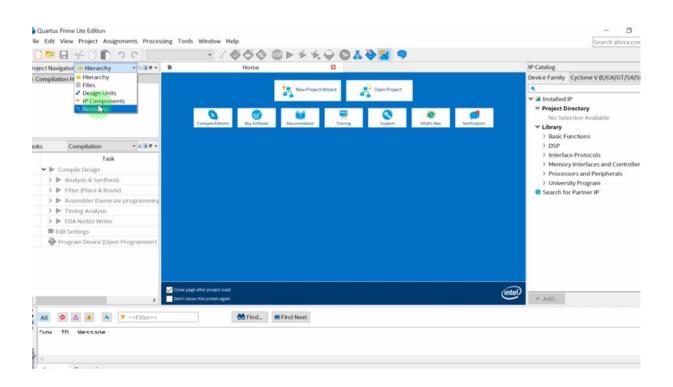

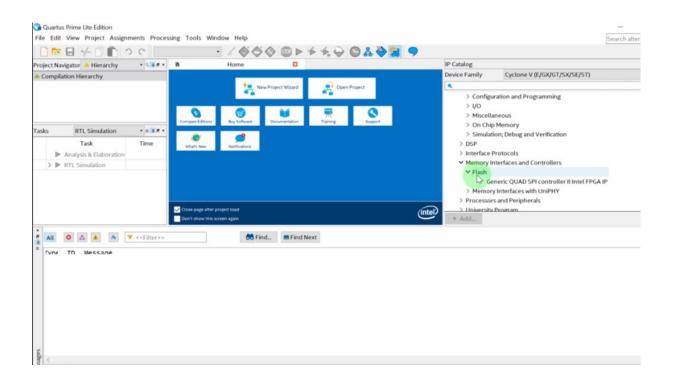

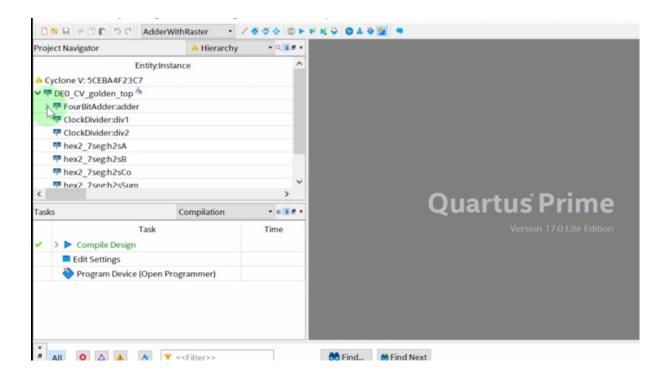

# WHERE EVERYTHING IS - PROJECT NAVIGATOR

So once installed quarters is ready to run any simulation project you want. So this is the welcome screen where you get to choose which project to open or to create a project and all of the things we have in these buttons right here. So right now there's no project open but let me show you where everything is so he read the left we have the project navigator. Where do you get to see all of the data regarding your open project.

And here we have a dropdown where you get to choose the aspects you want to see in the project navigator regarding your project. For example here we have hierarchy. You can see the files the design units the AP components and the revisions of your project. So it comes down to what you want to work with which level of abstraction you want to work if you want to simply see the files you can select files if you want to work with your units will you select hierarchy. That's why this is the default.

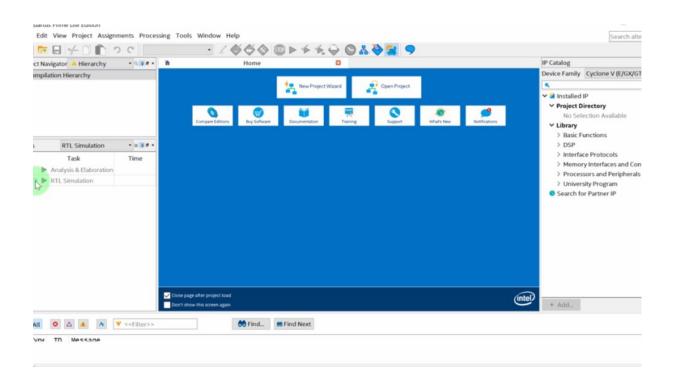

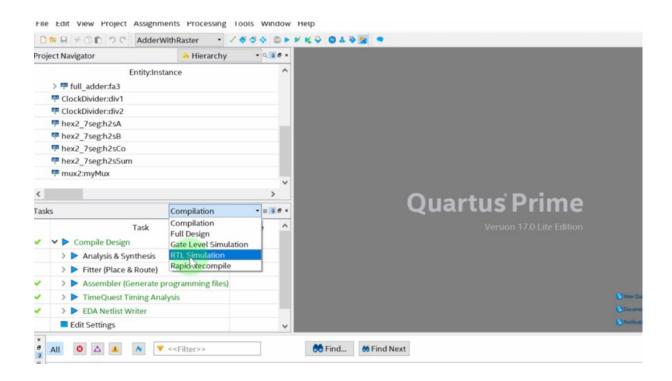

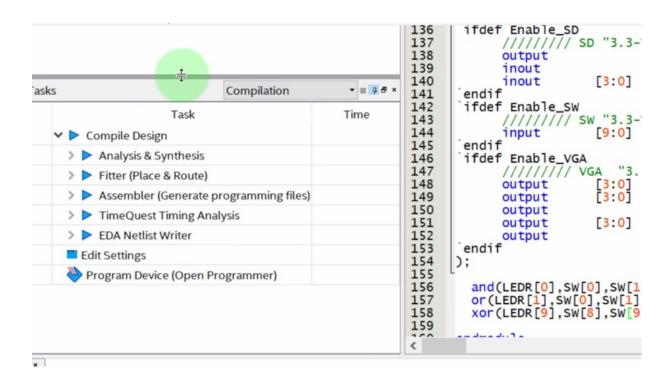

## WHERE EVERYTHING IS – TASKS

Next we have the task section here where you can find all of the steps of the synthesis or implementation process you want to perform. And like I mentioned before these steps depend on the objective of your project. So you get to choose that objective in this dropdown right here. So this is for compilation but we can also choose a full design a Gates level simulation on RTL simulation or a rapid recompile. And if you choose any of these elements you will see that the steps shown in this list will change. For example this is for a full design. And here we get compile design we get verified design export database archive project and as a final step in implementation we are usually interested in the programming file. So that's what this step is for. It says program device open programmer going back to the objectives of your project. We get a great level simulation where you get to finally run a simulation. We get to perform timing analysis and we get some steps all the way down to Gates level simulation.

However with the RTL simulation we get only one step after analysis and elaboration which is RTL simulation. Again the difference between RTL and gate level is that Gates level takes the lowest elements into account whereas RTL will base only the semantics of your very log or VH HDL design. Moving on at the bottom we have what we usually have in any idea which are the output sections. For example here we have the error messages warning messages some more warning messages. So these are critical warnings and these are all warnings and you also get to choose which messages you are seeing. So that's what these taps right here are for. Next we have at the middle. These buttons right here which are simply shortcuts to perform several operations since we don't have a project yet. This is like the welcome screen. It's called home. So we get to create a new project. We could open an existing project and we get a bunch of tools right here to assist you in your development process.

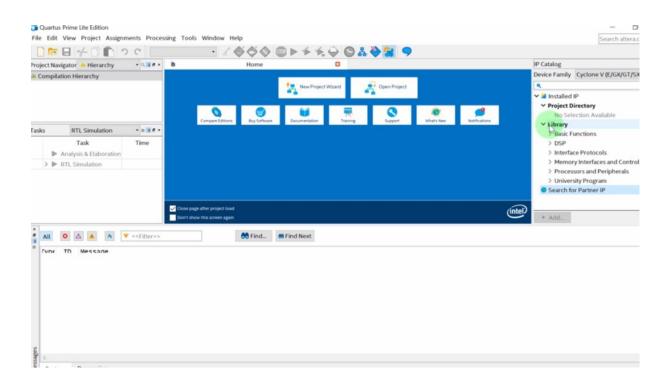

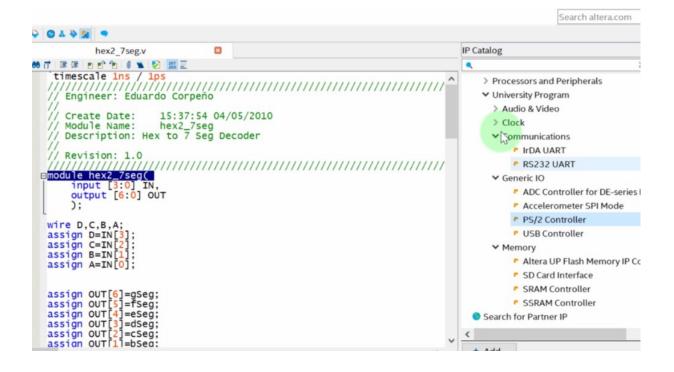

# WHERE EVERYTHING IS - IP CATALOG

At the right we have the AP catalog and this is very very cool. So you get to choose all of the AP that's available to you either with a license that's commercial IP or open source IP or even educational IP. So the structure goes like this. You have a top category right here that's called installed IP. You could search for partner IP this takes you to the intel Web site and you get to perform a search for IP. So there's a wide variety of elements available let's go back and looking at the installed IP you'll see that there's already a lot of IP available in the installation.

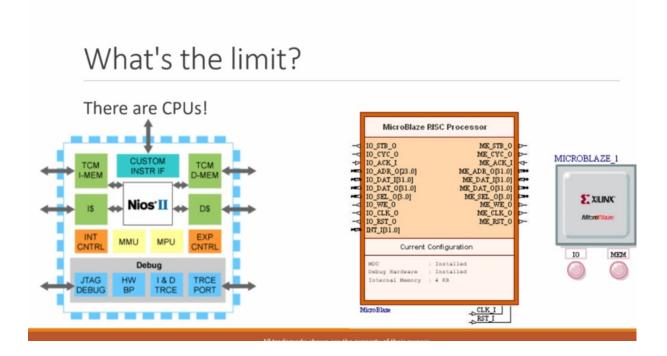

So here we have a project directory since we don't have any project open. Well nothing is shown here and then we have a library. So here we have basic functions arithmetic bridges and adapters clocks you name it. So let's see for example arithmetic we have let's say Altera floating point functions multiply other intel FPGA IP etc. We have memory interfaces and controllers for example here's something for a flash memory.

This is a generic quad spy controller but what I want to show you are these two elements processors and peripherals which are soft processors. So here we have code processors so here we have NEOs to custom instructions so here we have instructions you could make on your own for the NEOs too. Next we have heart processor components where you get to implement peripherals for heart process source that are included in your boards. And here we have peripherals. So we have a night to see slave an interrupt controller. And if all of this seems very limited to you. Well we have the university program section right here where we have a bunch of stuff for you to use freely with educational purposes. So here we have audio and video elements. We have clock elements communications generic IO and as you can see we have a U.S. B controller here for example. So you don't have to create your own and other memory we have a nice room controller. So this is a very nice library to start working with I.T..

## SETUP FOR IMPLEMENTATION

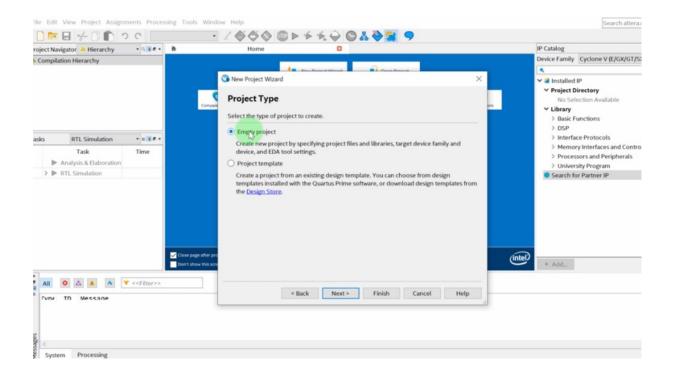

So if you want to create your implementation project to download your device into an FPGA you will need to do some setup. And for that you can ask to create a new project. Here we have some instructions and here you have to enter some things first your working directory. Second the name of your project. And finally the top level design entity of your project. That's the module that will be either downloaded to your FPGA or the top simulation module so let me create a directory called EDTA tools quarters. Let's name this project. My D 0 CV. Why. Because I'll be using a D 0 CV bought automatically the name of the project is copied to the top level module.

I'm okay with that. So this is where you get to download your templates for the board you are using if you want support for a development board so you can always create an empty project where you'll or all of the data by yourself. This will be kind of an advanced thing for you. So if you want to support your board for example that the e 0 CV by thoracic then I recommend you choose project template. Now let me read this part. It says create a project from an existing design template. You can choose from design templates installed with the quarter spraying software or download design templates from the design store. So if we click Next we'll see the design templates that are available in your installation. These are most likely up to date until the latest update you have performed on your software. So that's not always the best choice so I recommend that you go to the design store and download the latest support for your board. So let's see this link design store. This will take you to the intel Web site again. And here you can look for your board. So let's look for my these zero board which is a cyclone five. Let's see the categories available. We have designed examples and tutorials. Let's leave it at any.

| ts s | Solutions Support                               | inte                                                                           | ()                                                                                    |                             | US                 | A (English)  | Gigr          | n In     |

|------|-------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------|--------------------|--------------|---------------|----------|

| Lo   | oking for more design examples? Find them here. |                                                                                | Interested in con                                                                     | tributing co                | ontent to the      | design store | ? Click he    | re.      |

| Farr | nily: Cyclone V   Category: Any                 |                                                                                | Quartus Prim                                                                          | e Version:                  | Any 🔨              |              |               |          |

|      | velopment Kit: Any                              | <ul> <li>IP Co</li> </ul>                                                      | re: Any                                                                               |                             | *                  |              |               |          |

|      |                                                 |                                                                                |                                                                                       |                             |                    |              |               |          |

|      |                                                 |                                                                                |                                                                                       |                             |                    |              | Q Se          | ear      |

|      |                                                 |                                                                                |                                                                                       |                             | Quartus            |              |               |          |

| 1    | Name                                            | Category                                                                       | Development Kit                                                                       | Family                      | Prime 0<br>Version | Vendor       | Downloa       | ads      |

| *    |                                                 |                                                                                |                                                                                       | ¢<br>Family<br>Cyclone<br>V |                    | Vendor       | Downlos<br>66 |          |

|      | Name                                            | Category Design Example \ Outside Design                                       | Development Kit Cyclone V GT FPGA                                                     | Cyclone                     | Version            |              |               | ads<br>( |

| t    | Name<br>Gen2x4 AVMM DMA - Cyclone V             | Category Design Example \ Outside Design Store Design Example \ Outside Design | Development Kit<br>Cyclone V GT FPGA<br>Development Kit<br>Non kit specific Cyclone V | Cyclone<br>V<br>Cyclone     | Version<br>14.0.0  | Intel        | 66            | ,        |

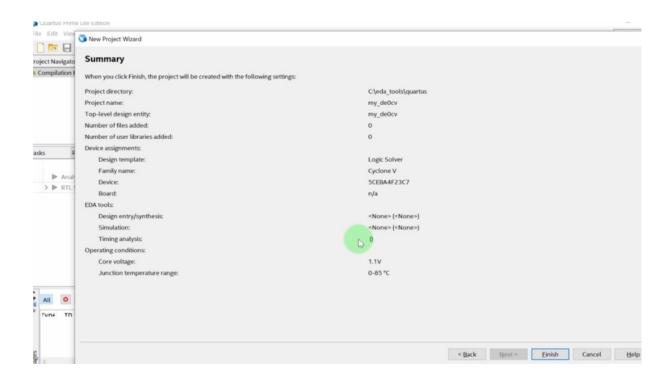

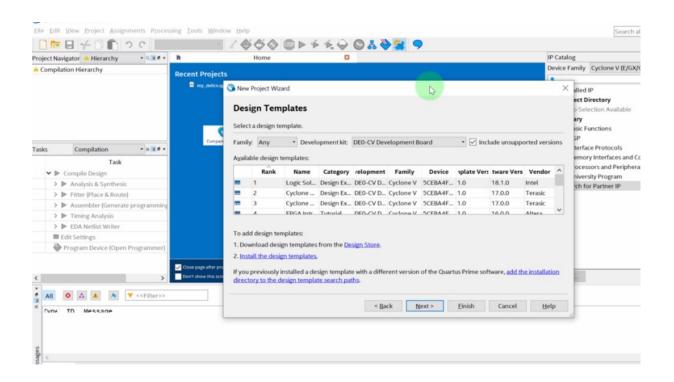

Let's see the quarter subprime version. We are using eighteen point one. And here we get to choose our board. So let's look for the easier aero CV development board right here and we also get to choose a knight core. We are not looking for anything in particular. So that's all we need. And here it is. It's this logic solver. This is an example. And it's for the DRC v Development Board. So all you have to do is click here on the name of the element and you'll get a download link. Right here. Notice that if we go back to quarters without downloading this we'll always get this part of the Wizard where you'll see the installed elements. Let's look at it at this point let's click next. So here we can see the supported elements. Let's see if we have the D 0 CV. Yes. Here it is.

| pilation Hierarchy    | Select  | a design te | emplate.   |            |           |            |           |            |            |         |                 |                | yclone V (E/           |

|-----------------------|---------|-------------|------------|------------|-----------|------------|-----------|------------|------------|---------|-----------------|----------------|------------------------|

|                       | Family  | Any         |            |            | •         | Developmen | tkit: Any |            |            | - 6     | Include unsuppo | orted versions |                        |

|                       | Availab | le design   | templates: |            |           |            |           |            |            |         |                 |                | sctory<br>tion Availab |

|                       |         | Rank        | Name *     | * Category | /elopment | Family     | Device    | plate Vers | tware Vers |         | Vendor          | ^              | aon Avanao             |

|                       | -       | 1           | Cyclone    | Design Ex  | DEO-CV D  | Cyclone V  | 5CEBA4F   | 1.0        | 17.0.0     | Terasic |                 |                | ctions                 |

|                       | -       | 2           | Cyclone    | Design Ex  | DEO-CV D  | Cyclone V  | 5CEBA4F   | 1.0        | 17.0.0     | Terasic |                 |                |                        |

| <b>RTL Simulation</b> |         | 3           | FPGA Intr  | Tutorial   | DEO-CV D  | Cyclone V  | 5CEBA4F   | 1.0        | 16.0.0     | Altera  |                 |                | Protocols              |

| Task                  | -       | 4           | Logic Sol  | Design Ex  | DEO-CV D  | Cyclone V  | 5CEBA4F   | 1.0        | 16.0.0     | Intel   |                 |                | nterfaces a            |

| Analysis & Elaborat   |         | 5           | Simple P   | Design Ex  | DEO-CV D  | Cyclone V  | 5CEBA4F   | 1.0        | 16.0.0     | Altera  |                 |                | rs and Peri            |

| RTL Simulation        | -       | 6           | Cyclone    | Design Ex  | DEO-CV D  | Cyclone V  | 5CEBA4F   | 1.0        | 16.0.0     | Terasic |                 |                | Partner IP             |

|                       | -       | 7           | Cyclone    | Design Ex  | Cyclone   | Cyclone V  | 5CGXFC5   | 1.0        | 17.0.0     | Altera  |                 |                | an creer to            |

|                       | -       | 8           | Cyclone    | Design Ex  | Cyclone   | Cyclone V  | 5CEFA7F   | 1.0        | 17.0.0     | Altera  |                 |                |                        |

|                       | -       | 9           | Cyclone    | Design Ex  | Cyclone   | Cyclone V  | 5CGTFD9   | 1.0        | 17.0.0     | Altera  |                 |                |                        |

|                       | -       | 10          |            |            |           |            | 5CSXFC6   |            | 17.0.0     | Altera  |                 |                |                        |

|                       |         | 11          |            |            |           |            | 5CEBA4F   |            | 17.0.0     | Terasic |                 |                |                        |

|                       |         | 12          |            |            |           |            | 5CSEMA    |            | 17.0.0     | Terasic |                 |                |                        |

|                       | -       | 13          | Cyclone    | Design Ex  | Cyclone   | Cyclone V  | 5CSXFC6   | 1.0        | 17.0.0     | Terasic |                 | ~              |                        |

So let me choose from this list. The zero CV Development Board. And these are all of the available elements as you can see there are several versions here. And the difference is not the template version. They are all 1.0. The difference is the software version. And as you can see the first two elements are virtually the same. There are no differences in their specification.

| ile Edit View   |     | w Pr   | oiect Wiz  | ard                                                                                                       |       |               |                            |          |        |                     |                 |                      |            | -              |

|-----------------|-----|--------|------------|-----------------------------------------------------------------------------------------------------------|-------|---------------|----------------------------|----------|--------|---------------------|-----------------|----------------------|------------|----------------|

| 📄 🗖 📄           |     |        |            |                                                                                                           |       |               |                            |          |        |                     |                 |                      |            |                |

| roject Navigato | De  | sig    | n Tem      | plates                                                                                                    |       |               |                            |          |        |                     |                 |                      |            |                |

| Compilation     | Sel | ecta   | design te  | molate                                                                                                    |       |               |                            |          |        |                     |                 |                      |            |                |

|                 |     |        |            |                                                                                                           |       |               |                            |          |        |                     |                 |                      |            |                |

|                 | Fan | nily:  | Any        | • Develo                                                                                                  | pme   | nt kit: DEO-0 | V Development Board        |          |        | •                   | Include unsu    | apported versi       | ons        |                |

|                 | Aya | ilable | e design t | emplates:                                                                                                 |       |               |                            |          |        |                     |                 |                      |            |                |

|                 |     |        | Rank       | Name                                                                                                      |       | Category      | Development Kit            | Fa       | mily   | Device              | mplate Versie   | ftware Versi         |            | Vendor         |

|                 | -   | 1      |            | Cyclone V DEO Development Board Baseline Pinout                                                           | De    | sign Example  | DE0-CV Developme           | Cyclo    | one V  | 5CEBA4F23C7         | 1.0             | 17.0.0               | Terasic    |                |

|                 |     | 2      |            | Cyclone V DEO Development Board Baseline Pinout                                                           | De    | sign Example  | DE0-CV Developme           | Cyclo    | one V  | 5CEBA4F23C7         | 1.0             | 17.0.0               | Terasic    |                |

| asks I          | F 📰 | 6      |            | Cyclone V DEO Development Board Baseline Pinout                                                           | De    | sign Example  | DE0-CV Developme           | Cycle    | ane V  | 5CEBA4F23C7         | 1.0             | 16.0.0               | Terasic    |                |

|                 | -   | 7      |            | Cyclone V DEO Development Board Baseline Pinout                                                           | De    | 🕞 Design 1    | emplate Installation       | $\times$ | ne V   | 5CEBA4F23C7         | 1.0             | 17.0.0               | Terasic    |                |

| ► Anal          | . = | 3      |            | FPGA Intro Example with PLL, Mux and Counter - DE0-C                                                      | V Tu  |               |                            |          | he V   | 5CEBA4F23C7         | 1.0             | 16.0.0               | Altera     |                |

| > > RTL         | -   | 4      |            | Logic Solver                                                                                              | De    | Design tem    | plate file (.par):         |          | he V   | 5CEBA4F23C7         | 1.0             | 16.0.0               | Intel      |                |

|                 | -   | 5      |            | Simple PWM Design w/ Cyclone DE0-CV                                                                       | De    |               |                            |          | he V   | 5CEBA4F23C7         | 1.0             | 16.0.0               | Altera     |                |

| -               | sup | porte  |            | scted design template is not supported in the current ver<br>n of the Quartus Prime software.<br>nplates: | ion c | Cheda_too     | OK Cance                   |          | e late | st version of the o | lesign template | from the <u>Desi</u> | gn Store ( | or use the     |

| All             |     |        | -          | gn templates from the <u>Design Store</u> .                                                               |       |               |                            |          |        |                     |                 |                      |            |                |

|                 | 5   |        |            | zn templates.                                                                                             |       |               |                            |          |        |                     |                 |                      |            |                |

| fvn≠ TD         |     |        |            | installed a design template with a different version of the                                               | Quar  | tus Prime sof | tware, add the installatio | n dire   | ctory  | to the design tem   | plate search pa | ths.                 |            |                |

| < Allow         |     |        |            |                                                                                                           |       |               |                            |          |        | < <u>B</u> ack      | Next >          | Einish               | Canc       | el <u>H</u> el |

So I can choose either of these two. This one says cyclone 5 the zero Development Board baseline burnout. So this has all of the spin assignments in the board for you to use on your top design. You could always use any of the others. And we even have an example design which is this logic solver. This is the one we saw online. So as you can see it's already installed. Let's go back to the browser and let's look at the version of this design so the design is also version 1.0. The device is five CB A4. That's the FPGA which is the same for all of these devices right here and the version of Cordis prime is eighteen point one. So what they are seeing here is that this version of the design is supported by our version of quietness. Once again there's no need to download it since we already have it here. Now that's not what it says right here. It says warning this elected the same template is not supported in the current version of the as spraying software download the latest version of the design template from the design store. So here are again the instructions to add design templates first download design templates from the design store second install the design templates. This is another link. And here you get to install them. You get a dot bar file. And here is where you will install it. That's the destination. Notice that the suggested

directory is the one for my project not the installation directory for quarters.

OK so let's go download that design and see how it looks in this list. Let's go back and download. We have to agree to some terms and we get to choose that file from courts. So here it is logic solver gooey duck bar. Let me click OK we get a message that the installation was successful and now the design should appear here. Let's select the D zero C.V. once more and here it is. Now it's the first one and you'll see that the software version is eighteen point one. Once again since the template version is 1 all we can understand by this is that this version was already supported but the download we just made informed the idea about this support. So I question how necessary that was. But for example if you have another board that is not listed in here or some example that is not in this installation you can always download it following these steps. That's why I've been showing you all of this. So let's click next and we get a summary so we get to click on finish after a while we get our design finally open in quarters. So at the left we get the hierarchy with the logic solver

shown right here. Remember this is an already made design so it has a bunch of code in very long and it's a nice application but it requires some explanation and I encourage you to go through the code and try to figure out what it does and maybe even download it to your DRM CV board if you have one. But for now let's see how we can make a design of our own.

# HELLO WORLD - CREATE A PROJECT

So now let's create a project of our own. And for that we need to click on new project wizard next. And a very important thing is that we are not supposed to work on the same directory for different projects. So I'll rename this the latest project was on a tool Skordas. So let me name this quietness.

Hello the project will be called Hello World. Next we'll create a project template again but this time we'll create an empty project for that the zero CV board. Well not exactly an empty project but the baseline keynote project once again we get the message that this is not supported by our version of quarters. But I say let's take our chances finish.

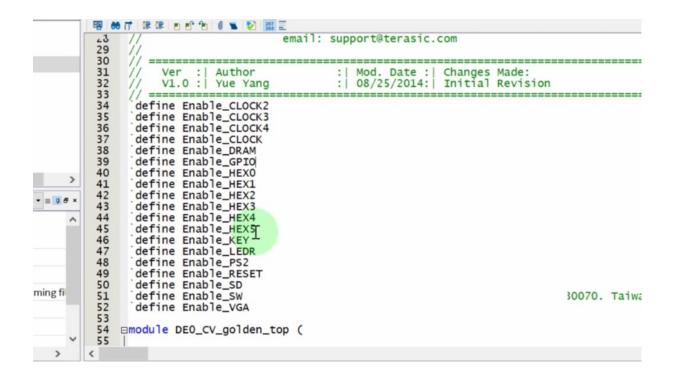

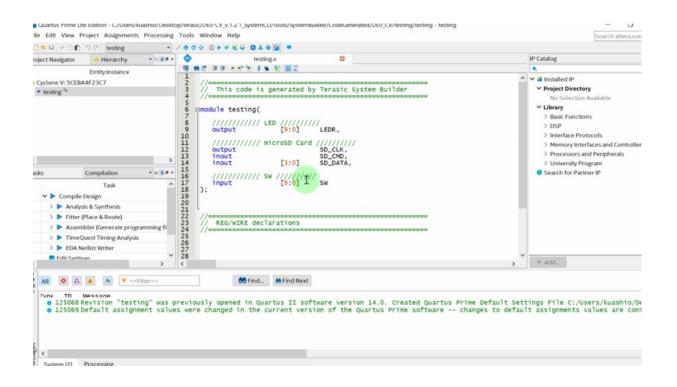

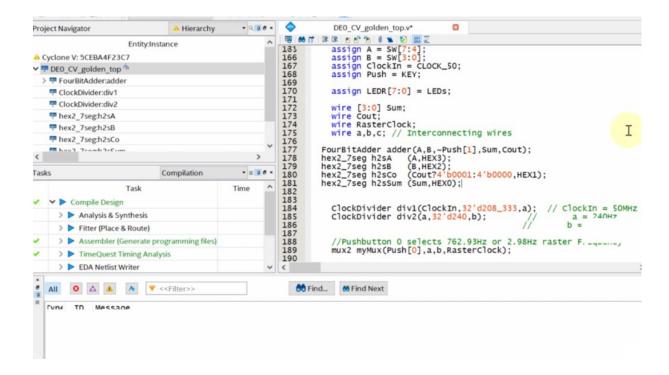

# HELLO WORLD - TOP MODULE SOURCE FILE

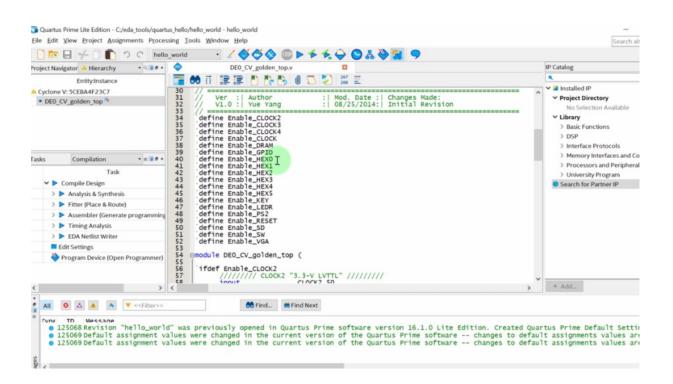

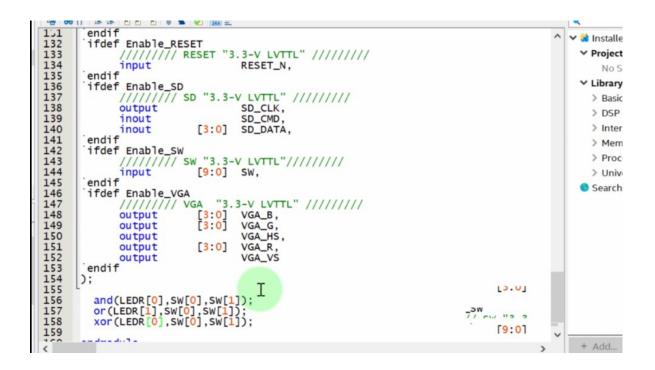

And in here we get one single design that says the zero CV golden top after opening it will see a big comment right here with the copyright and information about this project and then we have a bunch of defined statements which are very very useful they say define enable clock to clock three clock for enable every device on the board.

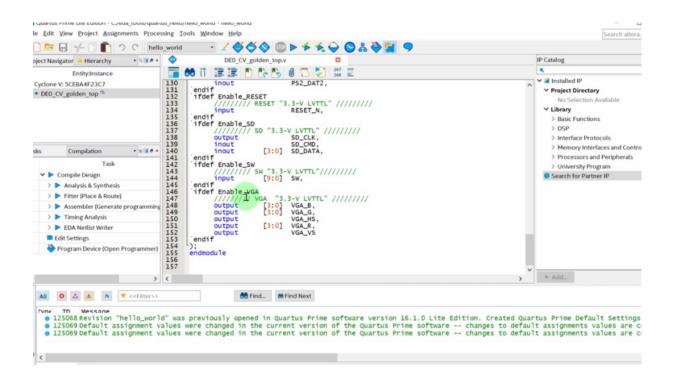

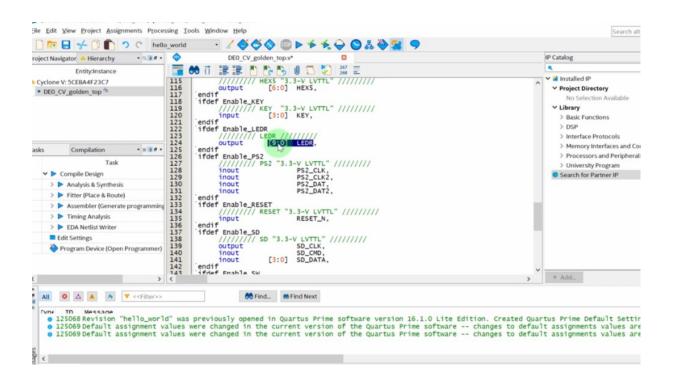

Hex 0 x 1 which are the hex displays enabled key for the key arrays or the buttons. We have the switches right here. Enable as W. ala the R which are D LCD onboard. And if you leave all of these defined will all of these elements will be included in your design and the way you a Yank did this is by entering. If def statements to include conditionally all of these parts or rather bought off your top design.

So this is a very elegant way of creating something flexible for everyone. So let's say we want to create a simple Hello World. By that I mean something that copies the states of the switches onto the LCD. So we only need the switches and the LCD if we want to do that then all we need are the switches which are these enable as W and the LCD D.R.. The rest should be commented out. So let me do that as you can see all I'm using are LCD are and S.W.. I don't have to delete anything here because this is all conditionally included with if def statements.

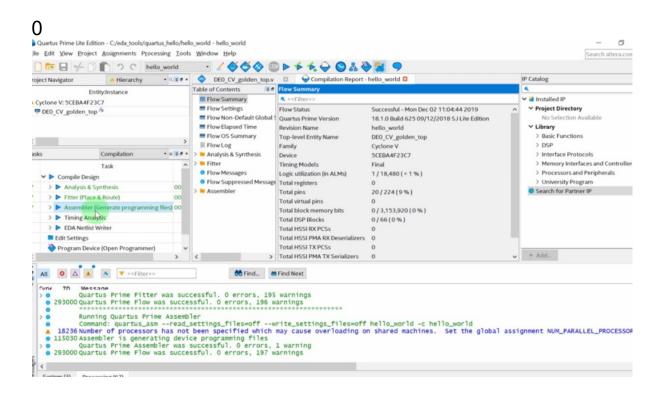

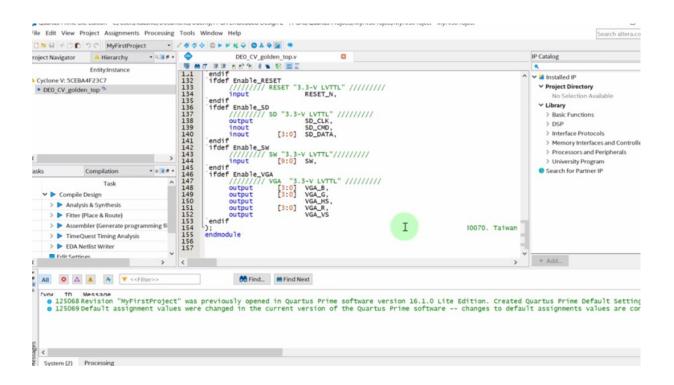

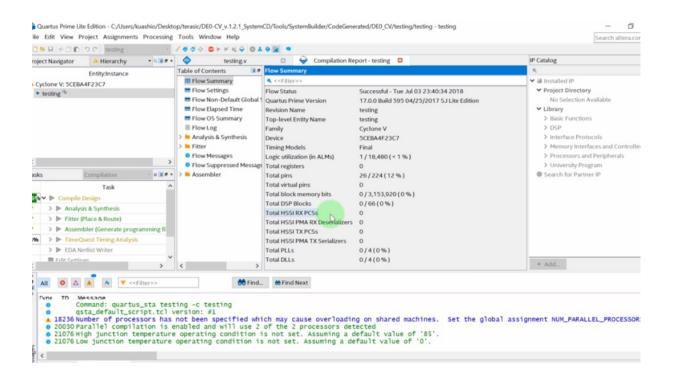

## HELLO WORLD – IMPLEMENTATION

And as you can see the module is empty. So let me open up some space here. And this will be very very simple. Let me just assign the D.R. to S. W.. I presume that's confirmed the names as W check. And early these are as you can see the LCD are 10 from 9 through 0 and the switches are also 10 from 9 through 0. That's it for our design. Now let's see how we can make it run. Remember that this is an already pre written project.

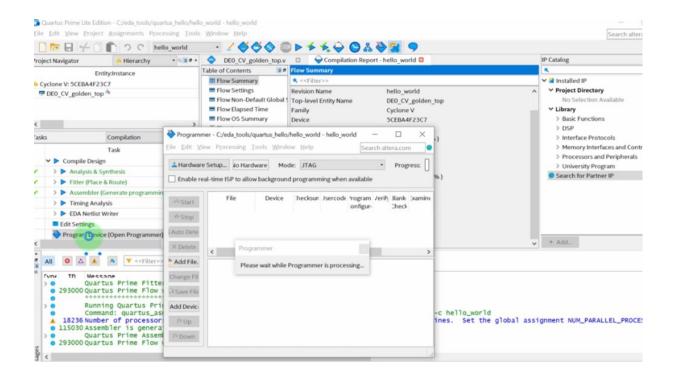

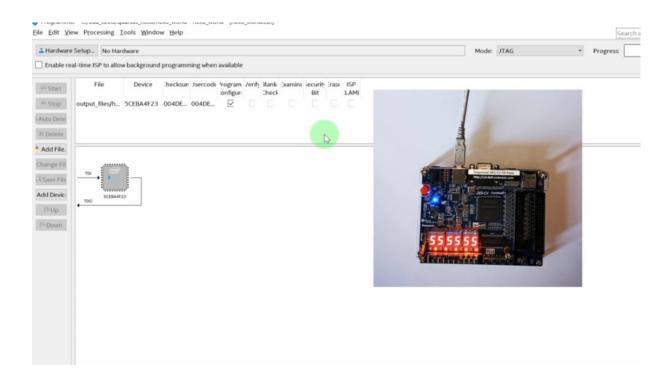

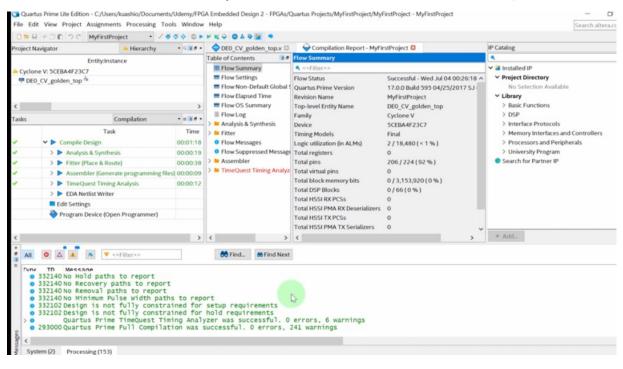

So Altera or intel must have gone through testing all of this code and we haven't done much programming here. We've only added one single statement which we are positive. It's correct. And so we'll get to pass all of the steps. So let's look at the left. We have compilation. This is the compilation purpose of the project and in the compilation purpose is where we get to program the device in the end. So we are good. This is what we want. Remember that we could select to perform only a simulation in the gate level or the RTL level.

| ject Navigator                                                                                                           | A Hierarchy                                                                                                             | • Q                                                                                                  | DE0_CV_golden_top.v                                                                                    | Compilation R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | eport - hello_world 🖾                                                                                                     | IP Catalog                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

|                                                                                                                          | Entity:Instance                                                                                                         |                                                                                                      | Table of Contents                                                                                      | Flow Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                           |                                                                                                    |

| Cyclone V: 5CEBA4F23C7<br>• DE0_CV_golden_top <sup>®</sup>                                                               |                                                                                                                         |                                                                                                      | Flow Summary     Flow Settings     Flow Non-Default Global S     Flow Elapsed Time     Flow OS Summary | Content of the second s | Flow Failed - Mon Dec 02 11:00:30 2019<br>18.1.0 Build 625 09/12/2018 SJ Lite Edition<br>hello_world<br>DE0_CV_golden_top | V al Installed IP     Vroject Directory     No Selection Available     Library     Sasic Functions |

| ks                                                                                                                       | Compilation                                                                                                             | - = <b>3</b> 0 ×                                                                                     | Flow Log                                                                                               | Family                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Cyclone V                                                                                                                 | > DSP                                                                                              |

|                                                                                                                          | Task                                                                                                                    |                                                                                                      | > Analysis & Synthesis                                                                                 | Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5CEBA4F23C7                                                                                                               | > Interface Protocols                                                                              |

| Compile Design      Analysis & Synthesis      OO      Fitter (Place & Route)      Assembler (Generate programming files) |                                                                                                                         |                                                                                                      | <ul> <li>Flow Messages</li> <li>Flow Suppressed Message</li> </ul>                                     | Timing Models<br>Cogic utilization (in ALMs)<br>Total registers<br>Total pins<br>Total virtual pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Final<br>N/A until Partition Merge<br>N/A until Partition Merge<br>N/A until Partition Merge<br>N/A until Partition Merge | <ul> <li>Memory Interfaces and Control</li> <li>Processors and Peripherals</li> </ul>              |

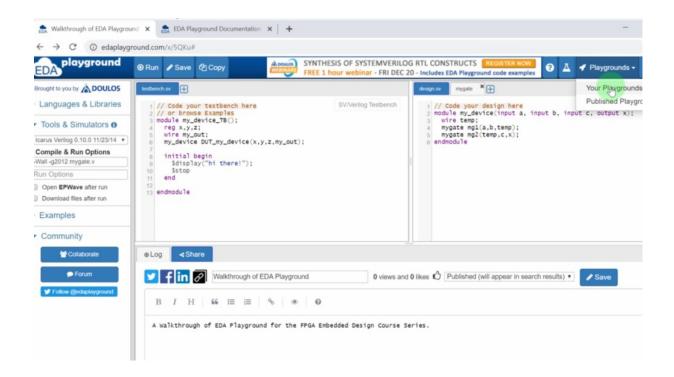

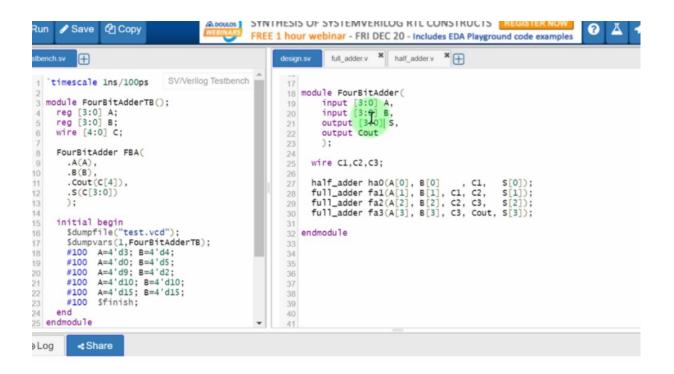

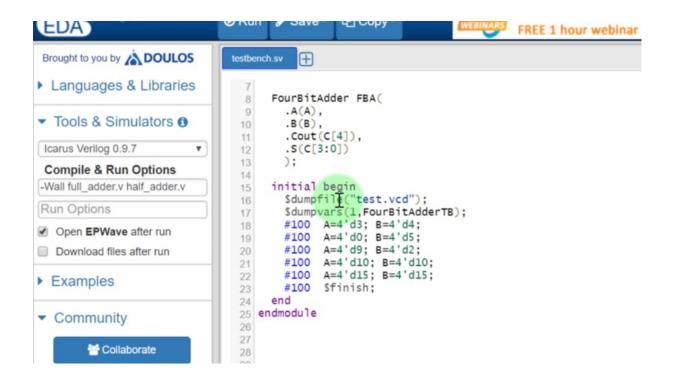

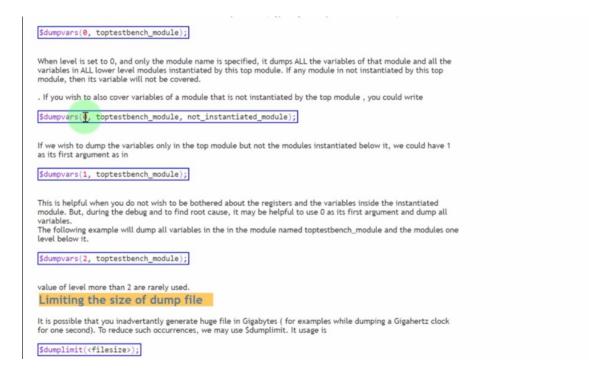

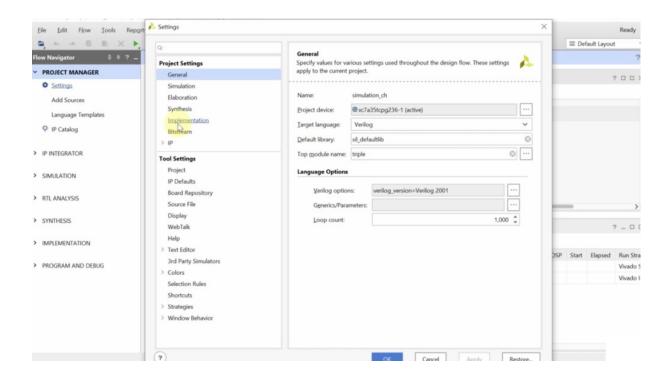

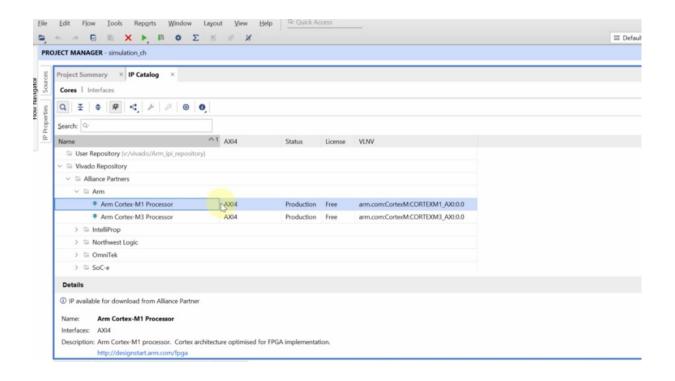

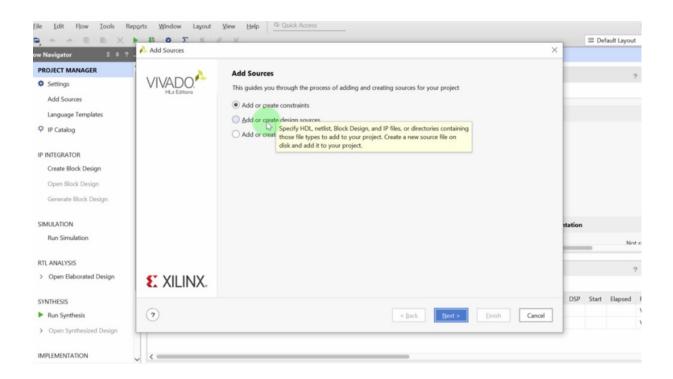

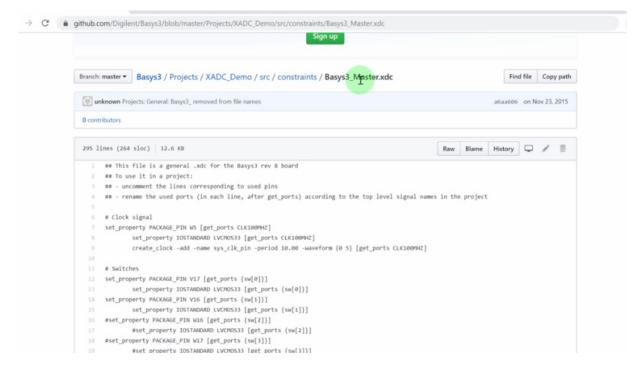

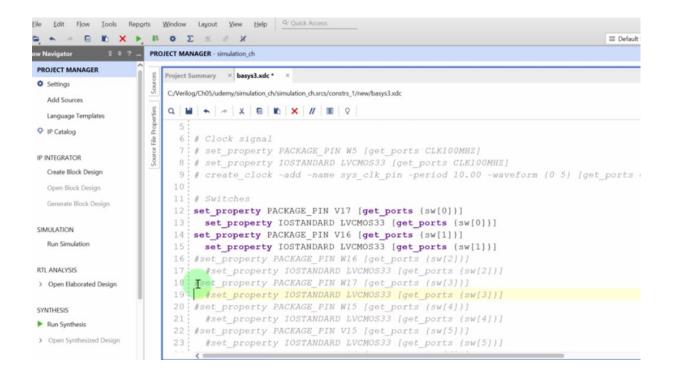

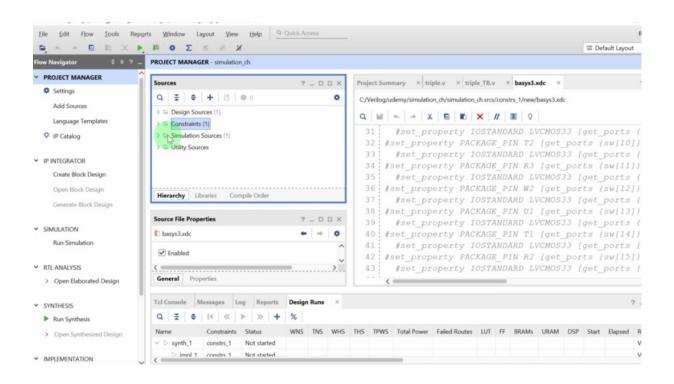

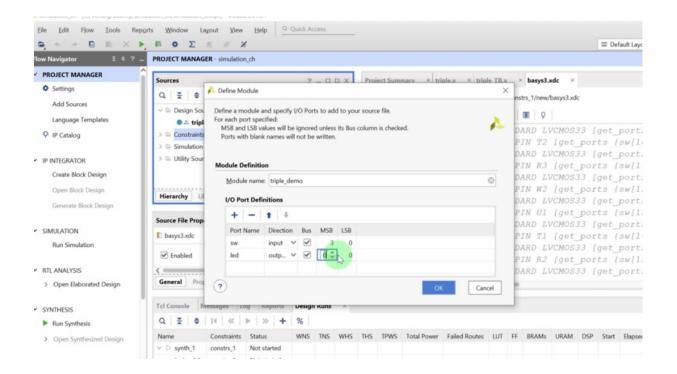

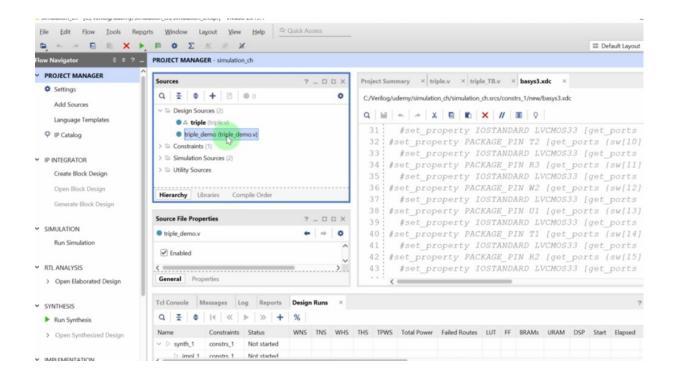

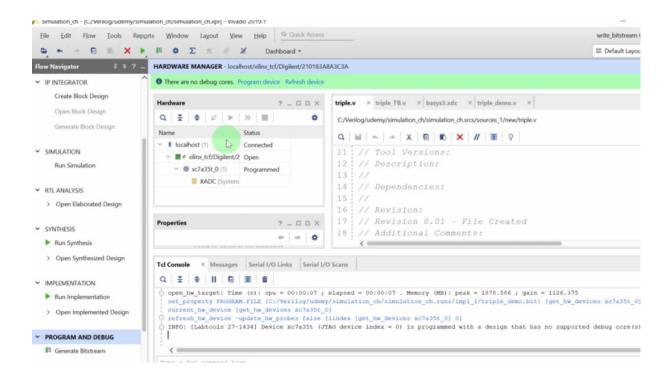

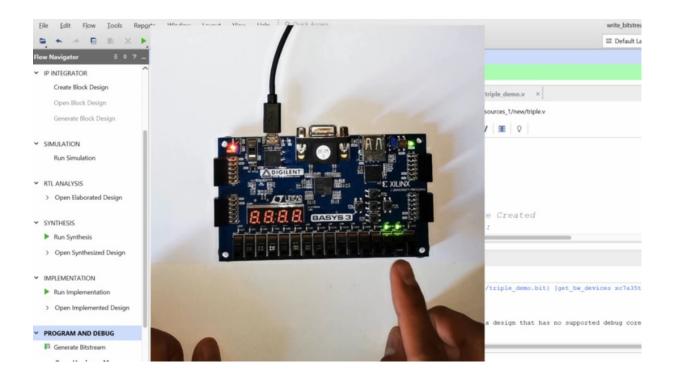

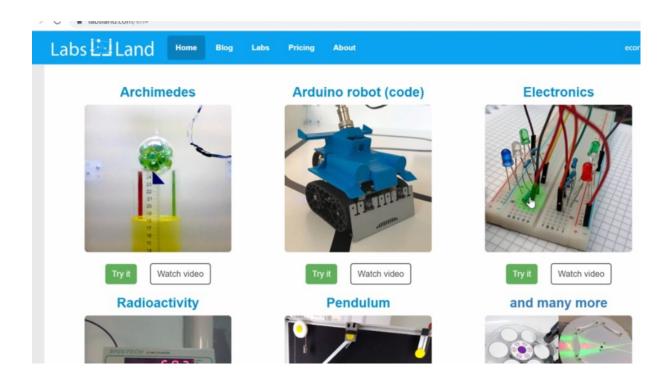

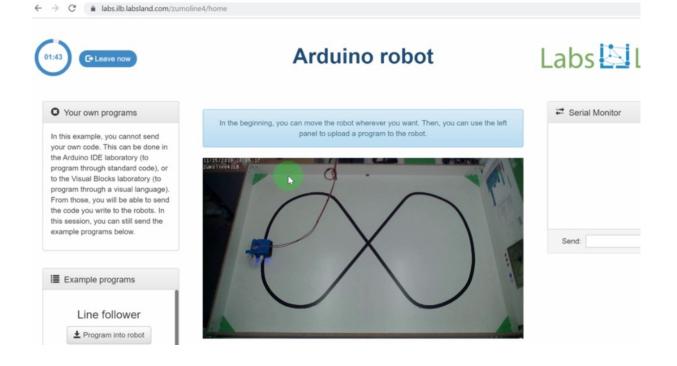

|                                                                                                                          |                                                                                                                         |                                                                                                      | • How Suppressed Pressage                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                           | > University Program                                                                               |