САНКТ-ПЕТЕРБУРГСКИЙ ПОЛИТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ ПЕТРА ВЕЛИКОГО

Д. В. Морозов М. М. Пилипко М. С. Енученко

# СХЕМОТЕХНИКА ЦИФРОВЫХ УСТРОЙСТВ КОМБИНАЦИОННЫЕ И ПОСЛЕДОВАТЕЛЬНОСТНЫЕ СХЕМЫ

Учебное пособие

Санкт-Петербург 2022 УДК 004.31: 621.382.2/.3 ББК 32.852.8:32.847:32.971 M80

Морозов Д. В. Схемотехника цифровых устройств. Комбинационные и последовательностные схемы: учеб. пособие / Д. В. Морозов, М. М. Пилипко, М. С. Енученко. – СПб., 2022. – 106 с.

Соответствует содержанию «Схемотехника цифровых дисциплины устройств» Федерального образовательного стандарта высшего образования по направлению подготовки 11.03.04 «Электроника и наноэлектроника». Изложены основные сведения построению цифровых схем металл-оксид-ПО на полупроводник (МОП) транзисторах. Рассмотрены структура, принцип действия, вольт-амперные характеристики и эквивалентные схемы МОП-транзисторов. Представлены основы алгебры логики, логические элементы и комбинационные цифровые схемы: инвертор, «И-НЕ», «ИЛИ-НЕ», «И-ИЛИ-НЕ», «ИЛИ-И-НЕ», «исключающее ИЛИ», «исключающее ИЛИ-НЕ», мультиплексоры и сумматоры. Описана реализация схем с использованием транзисторов с дополнительным управлением по стоку или истоку. Приводятся последовательностные цифровые схемы – триггеры, регистры и счётчики. Использование материала учебного пособия должно исключить боль и слезы при изучении дисциплины.

Предназначено для студентов, обучающихся по направлению подготовки 11.03.04 «Электроника и наноэлектроника».

Табл. 26. Ил. 85. Библиогр.: 10 назв.

# ОГЛАВЛЕНИЕ

| ,  |

|----|

| )  |

| ,  |

| ,  |

|    |

| )  |

| 1  |

| 2  |

| 2  |

| 6  |

| 9  |

| 23 |

| 6  |

|    |

| 9  |

| 1  |

|    |

| 1  |

| 5  |

| 6  |

|    |

| 0  |

|    |

| -2 |

|    |

| 4  |

| 6  |

| 2  |

| 3  |

| 3  |

| 5  |

| 6  |

| 2  |

| 4  |

| 5  |

| 5  |

| 9  |

| 1  |

|    |

| 3.3.4. <i>D</i> -триггер на основе проходных транзисторов | 77  |

|-----------------------------------------------------------|-----|

| 3.3.5. <i>JK</i> -триггер                                 | 79  |

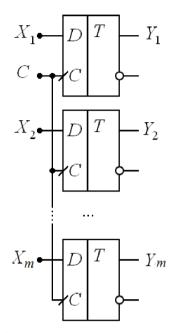

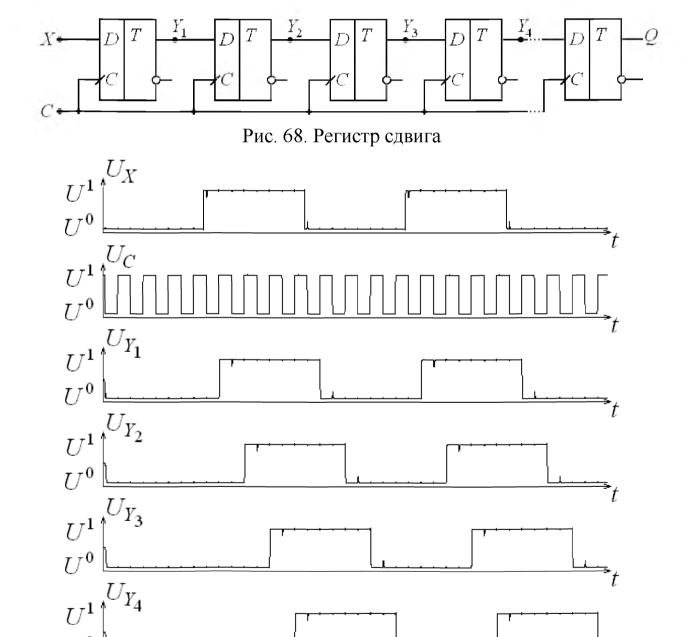

| 3.4. Регистры                                             | 81  |

| 3.4.1. Параллельный регистр                               | 82  |

|                                                           | 84  |

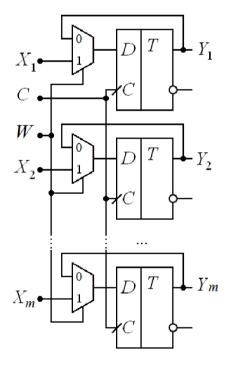

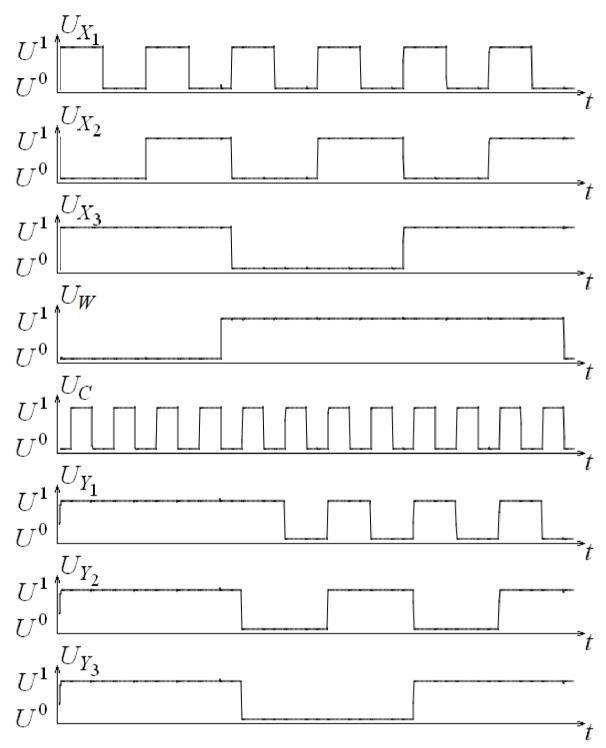

| 3.4.3. Реверсивный регистр сдвига                         | 86  |

| 3.4.4. Параллельно-последовательный регистр               | 87  |

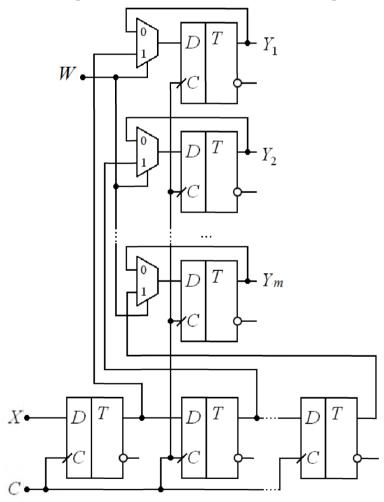

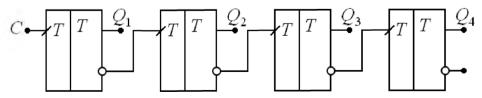

| 3.4.5. Последовательно-параллельный регистр               | 89  |

| 3.5. Счётчики                                             | 90  |

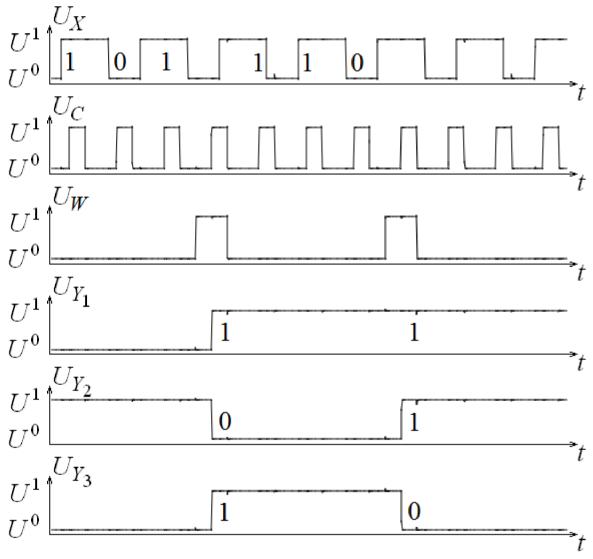

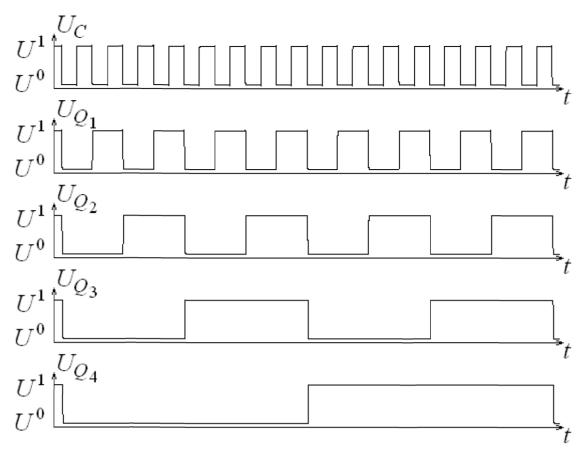

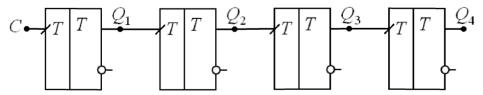

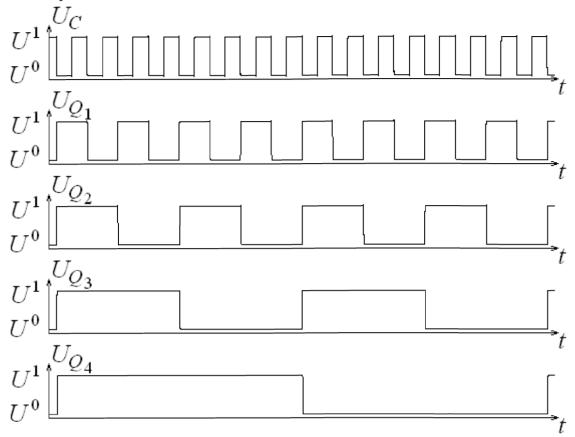

| 3.5.1. Двоичные счётчики                                  | 91  |

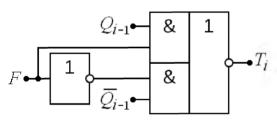

| 3.5.2. Счётчики с произвольным коэффициентом              |     |

| пересчёта                                                 | 96  |

| 3.6. Потребляемая мощность цифровой схемы                 | 101 |

| 3.7. Вопросы для самопроверки                             | 105 |

| Библиографический список                                  | 106 |

|                                                           |     |

# СПИСОК ПРИНЯТЫХ СОКРАЩЕНИЙ

BX - вход;

ВЫХ – выход;

ДИН – динамическая;

ЗД – задержка;

МОП – металл-оксид-полупроводник;

КМОП – комплементарный металл-оксид-полупроводник;

ПИТ – питание;

ПОТР – потребляемая;

СДНФ – совершенная дизъюнктивная нормальная форма;

СКВ – сквозной;

СКНФ – совершенная конъюнктивная нормальная форма;

СР – средняя;

СТАТ – статическая.

# **ВВЕДЕНИЕ**

B учебном пособии изложены основные сведения ПО построению цифровых схем на металл-оксид-полупроводник (МОП) транзисторах. В первом разделе рассмотрены структура и принцип действия МОП-транзистора. Обсуждается работа МОП-транзисторов с индуцированными каналами *n*- и *p*-типа при воздействии различных напряжений сток-исток и затвор-исток. Приведены аппроксимации стока. Представлены параметры МОП-транзистора. Показаны передаточные и выходные статические характеристики. Введены условные обозначения МОП-транзисторов.

Во втором разделе рассматриваются комбинационные цифровые Обсуждается схемы. схема комплементарного инвертора. Представлены передаточная характеристика, малосигнальная эквивалентная схема и проведена оценка запаса помехоустойчивости. Изложены основы алгебры логики. Объясняется работа логических элементов и комбинационных схем: инвертор, «И-НЕ», «ИЛИ-НЕ», «И-ИЛИ-НЕ», «ИЛИ-И-НЕ», «исключающее ИЛИ», «исключающее ИЛИ-НЕ», мультиплексоры и сумматоры. Описана реализация схем на транзисторном уровне, в том числе с использованием МОПтранзисторов с дополнительным управлением по стоку или истоку. Показаны сигналы в схемах во временной области. Представлены условные обозначения логических элементов.

В третьем разделе обсуждаются последовательностные цифровые схемы – триггеры, регистры и счётчики. Рассматриваются RS-, RCS-, T-, D- и JK-триггеры; параллельные, последовательные, параллельно-последовательные, последовательно-параллельные реверсивные регистры сдвига; суммирующие, вычитающие, реверсивные, двоично-десятичные и с произвольным коэффициентом пересчёта, счётчики c последовательным переносом. Представлены параллельным реализации последовательностных схем на уровне логических элементов, приведены условные обозначения и показаны сигналы в схемах во временной области.

# 1. МЕТАЛЛ-ОКИД-ПОЛУПРОВОДНИК ТРАНЗИСТОРЫ

# 1.1. СТРУКТУРА И ПРИНЦИП ДЕЙСТВИЯ

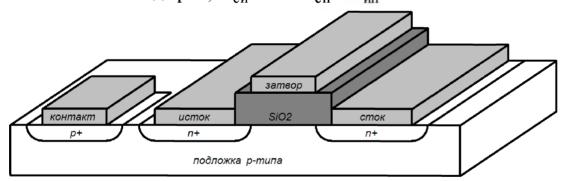

Структура металл-оксид-полупроводник (МОП) транзистора с индуцированным каналом *п*-типа [1, 2] показана на рис. 1. Пластина полупроводника p-типа называется подложкой ( $\Pi$ ). Электрод для создания поля является затвором (3). Два других электрода называют стоком (С) и истоком (И). Поскольку структура симметрична, то сток и исток взаимозаменяемы. Стоком является тот, на который при соответствующей полярности напряжения поступают рабочие носители заряда. Если канал *п*-типа, то рабочие носители – электроны, полярность напряжения сток-исток  $U_{\rm cu}$  положительная и относительно напряжения на подложке  $U_{\rm cn} > U_{\rm ип}$ . В случае МОПтранзистора с индуцированным каналом р-типа, подложка п-типа, рабочие носители – дырки,  $U_{cu} < 0$  и  $U_{cn} < U_{un}$ .

Рис. 1. МОП-транзистор с индуцированным каналом n-типа

Транзистор, показанный на рис. 1, работает следующим образом. Пусть затвор соединён с истоком, т.е. разность потенциалов затвор-исток  $U_{\rm 3H}=0$ . При этом канал отсутствует. Поэтому при подаче напряжения сток-исток  $U_{\rm cu}$  ток в цепи стока  $I_{\rm c}$  будет определяться лишь утечками и будет ничтожно мал. Если подать на затвор-исток отрицательное напряжение  $U_{\rm 3H}<0$ , то слой полупроводника обогатится дырками, при этом ток в стоковой цепи по-прежнему будет определяться утечками. Если же подавать на

затвор-исток возрастающее положительное напряжение  $U_{\rm 3u}>0$ , то сначала образуется обеднённый слой дырок, а затем при превышении порогового напряжения — слой электронов, т.е. проводящий канал. При этом ток стока  $I_{\rm c}$  будет зависеть от значения напряжения  $U_{\rm 3u}$ .

Каналы, отсутствующие В равновесном состоянии И образующиеся под действием внешнего напряжения, называют Напряжение индуцированными. затвор-исток, котором образуется канал, является пороговым напряжением отпирания транзистора и обозначается  $U_0$ . Длина канала L равна расстоянию между проводниками истока и стока, а ширина W – протяжённости Если проводников. рассматривать МОП-транзистор ЭТИХ индуцированным каналом р-типа, то для такой структуры характерны обратные полярности порогового и рабочих напряжений:  $U_{\rm o} < 0$ ,  $U_{\rm 3H} < 0$ ,  $U_{\rm CH} < 0$ . Схемы, в которых используется сочетание МОПтранзисторов с каналами *n*- и *p*-типа, называют комплементарными.

Рассмотрим МОП-транзистор с индуцированным каналом *п*типа. Если напряжение  $U_{cu} = 0$ , то поверхность полупроводника эквипотенциальна, поле в диэлектрике однородное, и толщина образовавшегося канала одинакова на всем протяжении. Если же протекает ток стока,  $U_{cu} > 0$ , To И потенциал поверхности полупроводника возрастает от истока к стоку. Значит, разность потенциалов между затвором и поверхностью полупроводника в уменьшается. Соответственно уменьшаются направлении стока напряжённость поля в диэлектрике и удельный заряд электронов в канале. Поэтому сечение канала в глубину вблизи стока сужается.

При некотором критическом напряжении сток-исток, которое называют напряжением насыщения  $U_{\rm син}$ , разность потенциалов между затвором и истоком становится равной пороговому напряжению  $U_{\rm син} = U_{\rm 3u} - U_{\rm o}$ . При  $U_{\rm cu} > U_{\rm cuh}$  слой объёмного заряда начинает выходить на поверхность вблизи стока, вследствие этого, происходит укорочение длины канала. В насыщении ток стока практически перестаёт зависеть от напряжения  $U_{\rm cu}$ .

# 1.2. ВОЛЬТ-АМПЕРНЫЕ ХАРАКТЕРИСТИКИ И ЭКВИВАЛЕНТНЫЕ СХЕМЫ

Вольт-амперная характеристика МОП-транзистора [1, 2] при условии  $U_{\rm cu} < U_{\rm cu\, H}$  аппроксимируется выражением:

$$I_{\rm c} = 2k \bigg[ (U_{\rm 3M} - U_{\rm o}) U_{\rm cM} - \frac{1}{2} U_{\rm cM}^2 \bigg], \qquad k = \frac{1}{2} \mu C_o \frac{W}{L},$$

где k — коэффициент проводимости,  $\mu$  — приповерхностная подвижность носителей заряда,  $C_o$  — удельная ёмкость диэлектрика. При  $U_{\rm cu}$  <<  $U_{\rm 3u}$  —  $U_{\rm o}$  выражение принимает вид:

$$I_{\rm c} = 2k(U_{\rm _{3H}} - U_{\rm _{O}})U_{\rm _{CH}},$$

где коэффициент при  $U_{\mathrm{cu}}$  является проводимостью канала сток-исток:

$$g_m = 2k(U_{3H} - U_0)$$

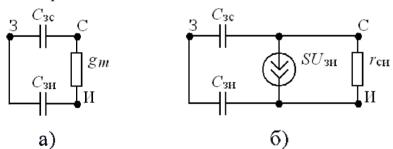

При этом с точки зрения эквивалентной схемы МОП-транзистор (без учёта подложки) представляет включённую между стоком и истоком управляемую проводимость  $g_m$ , прямо пропорциональную напряжению  $U_{3\rm H}$  (рис. 2, a)). Ёмкости  $C_{3\rm C}$  и  $C_{3\rm H}$  — это ёмкости перекрытий затвора относительно стока и истока.

Рис. 2. Эквивалентные схемы МОП-транзистора

Если же  $U_{\rm cu}>U_{\rm cuh}$ , то ток стока остаётся близким тому значению, которое имеет при  $U_{\rm cu}=U_{\rm cuh}$ . Поэтому вольт-амперную характеристику МОП-транзистора в насыщении можно записать как:

$$I_{c} = k(U_{3H} - U_{0})^{2}$$

.

Малосигнальными параметрами в насыщении являются:

— крутизна

$$S = \frac{dI_{\rm c}}{dU_{\rm 3H}}\bigg|_{U_{\rm cH} = {\rm const}};$$

— внутреннее сопротивление

$$r_{\rm cu}=rac{dU_{

m cu}}{dI_{

m c}}igg|_{U_{

m 3M}={

m const}}$$

— коэффициент усиления

$$Sr_{\rm cu} = \frac{dU_{\rm cu}}{dU_{\rm 3u}} \bigg|_{I_{\rm c}={\rm const}}$$

.

Крутизна имеет выражение:

$$S = 2k(U_{3H} - U_{0}) = 2\sqrt{kI_{c}}$$

.

Малосигнальная эквивалентная схема МОП-транзистора в насыщении (без учёта подложки) показана на рис. 2,  $\delta$ .

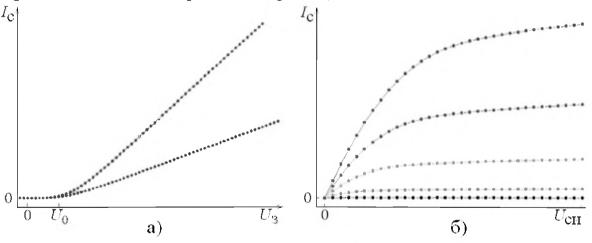

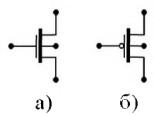

Пример статических вольт-амперных характеристик МОП-транзистора с индуцированным каналом n-типа показан на рис. 3 (рис. 3, a — передаточные, рис. 3,  $\delta$  — выходные) [1, 2]. Условные обозначения МОП-транзисторов с индуцированными каналами n-типа и p-типа показаны на рис. 4, a и рис. 4,  $\delta$  соответственно.

Рис. 3. Вольт-амперные характеристики МОП-транзистора с индуцированным каналом *n*-типа

Рис. 4. Условные обозначения МОП-транзисторов с индуцированными каналами n-типа (а) и p-типа (б)

### 1.3. ВОПРОСЫ ДЛЯ САМОПРОВЕРКИ

- 1. Нарисуйте структуру МОП-транзистора. Обозначьте напряжения сток-исток и затвор-исток. Изобразите канал.

- 2. Какими носителями заряда обусловлен ток в структуре МОПтранзистора? Если МОПтранзистор имеет индуцированный канал *п*типа, то какие носители заряда являются рабочими для такой структуры? Какова полярность напряжений сток-исток и затвористок?

- 3. Если затвор МОП-транзистора соединён с истоком, то чем определяется ток стока? Что такое индуцированный канал? Если МОП-транзистор имеет индуцированный канал *n*-типа и напряжение затвор-исток отрицательное, то как работает транзистор?

- 4. При каких напряжениях на электродах в МОП-транзисторе с индуцированным каналом n-типа (p-типа) образуется канал? Что такое пороговое напряжение отпирания МОП-транзистора? Какую полярность оно имеет для транзистора с индуцированным каналом n-типа (p-типа)?

- 5. Если сток МОП-транзистора соединён с истоком, то образуется ли канал? Что является длиной, а что шириной канала МОП-транзистора?

- 6. Если МОП-транзистор имеет индуцированный канал *п*-типа и напряжение сток-исток положительное, то какие характерные особенности имеет канал? Какой зависимостью определяется ток стока? Какой эквивалентной схемой может быть замещён транзистор?

- 7. Что происходит, когда МОП-транзистор входит в насыщение? Какой зависимостью определяется ток стока? Какой эквивалентной схемой может быть замещён транзистор?

- 8. Нарисуйте вид статических вольт-амперных характеристик МОП-транзистора с каналом n-типа (p-типа).

- 9. Объясните малосигнальные параметры МОП-транзистора.

- 10. Как называются схемы, в которых используется сочетание МОП-транзисторов с каналами n- и p-типа?

## 2. КОМБИНАЦИОННЫЕ ЦИФРОВЫЕ СХЕМЫ

# 2.1. КОМПЛЕМЕНТАРНЫЙ ИНВЕРТОР

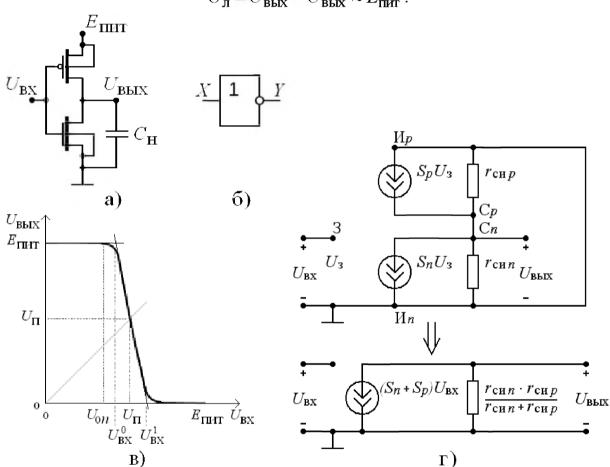

Рассмотрим схему комплементарного инвертора [2] с ёмкостной нагрузкой  $C_{\rm H}$ , показанную на рис. 5, a. Схема имеет однополярное положительное питание  $E_{\rm пит}$ , входное напряжение обозначено  $U_{\rm вx}$ , а выходное —  $U_{\rm выx}$ . Условное обозначение логического элемента приведено на рис. 5,  $\delta$ , где X — вход, а Y — выход.

Передаточная характеристика схемы комплементарного инвертора показана на рис. 5,  $\epsilon$ . На горизонтальных участках характеристики схема работает, как представлено на рис. 6 (где  $R_p$  и  $R_n$  — сопротивления открытых МОП-транзисторов с каналами p- и n-типа соответственно):

$$\begin{split} U_{\text{BX}} &= E_{\text{ПИТ}} = U^1 \Rightarrow U_{\text{ЗИ}n} = E_{\text{ПИТ}} > U_{\text{O}\,n}, \ U_{\text{ЗИ}\,p} = 0 > U_{\text{O}\,p} \Rightarrow U_{\text{ВЫХ}} = 0 = U^0 \,; \\ U_{\text{BX}} &= 0 = U^0 \Rightarrow U_{\text{ЗИ}\,n} = 0 < U_{\text{O}\,n}, \ U_{\text{ЗИ}\,p} = -E_{\text{ПИТ}} < U_{\text{O}\,p} \Rightarrow U_{\text{ВЫХ}} = E_{\text{ПИТ}} = U^1 \,. \end{split}$$

На наклонном участке передаточной характеристики рис. 5,  $\epsilon$  вблизи порогового напряжения переключения  $U_{\rm n}$  оба МОП-транзистора находятся в насыщении:

$$\begin{split} I_{\text{c}\,n} &= k_n (U_{\Pi} - U_{\text{o}\,n})^2 \, ; \; I_{\text{c}\,\,p} = k_p (E_{\text{пит}} - U_{\Pi} + U_{\text{o}\,p})^2 \, ; \\ I_{\text{c}\,n} &= I_{\text{c}\,p} \, ; \; U_{\Pi} = \frac{U_{\text{o}\,n} + \sqrt{k_p / k_n} (E_{\text{пит}} + U_{\text{o}\,p})}{1 + \sqrt{k_p / k_n}} \, . \end{split}$$

Малосигнальная эквивалентная схема по постоянному току на наклонном участке передаточной характеристики вблизи напряжения  $U_{\rm n}$  показана на рис. 5,  $\it e$ . Определим коэффициент усиления:

$$K_U = \frac{U_{\text{вых}}}{U_{\text{вх}}} = -(S_n + S_p) \frac{r_{\text{си}n} r_{\text{си}p}}{r_{\text{си}n} + r_{\text{си}p}} = \frac{-(S_n + S_p) r_{\text{си}n}}{1 + r_{\text{си}p} / r_{\text{си}p}},$$

Полагая, что  $S_n \cong S_p$  и  $r_{\operatorname{cu} n} \cong r_{\operatorname{cu} p}$ , получим:

$$K_U \approx -S_n r_{\text{CM}n}$$

.

Оценим запас помехоустойчивости (noise margin) схемы по передаточной характеристике рис. 5, в. Входные напряжения

логического нуля и единицы обозначены  $U_{\rm Bx}^0$  и  $U_{\rm Bx}^1$  соответственно, а выходные  $U_{\rm Bbix}^0$  и  $U_{\rm Bbix}^1$ . Запас помехоустойчивости по уровням логического нуля  $NM^0$  и логической единицы  $NM^1$  можно выразить следующим образом:

Логический перепад схемы определяется как:

$$U_{\mathrm{JI}} = U_{\mathrm{BЫX}}^{\mathrm{l}} - U_{\mathrm{BЫX}}^{\mathrm{0}} \approx E_{\mathrm{ПИТ}}$$

.

Рис. 5. Комплементарный инвертор

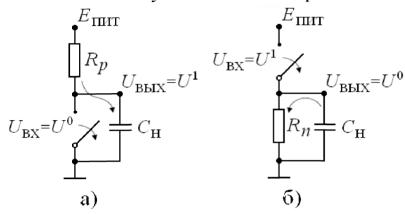

Комплементарный инвертор является простейшей цифровой схемой. Сигналы в схеме во временной области представлены на рис. 7. Уменьшение потребляемой мощности, обусловленной сквозным током  $I_{\rm скв}$  через оба транзистора при переключениях схемы, возможно за счёт снижения напряжения питания до величин

$E_{\text{пит}} < U_{\text{о}\,n} - U_{\text{о}\,p}$ , тогда в один момент времени транзисторы с каналами p- и n-типа не смогут оказаться в открытом состоянии.

Рис. 6. Разряд и заряд нагрузочной ёмкости комплементарного инвертора

Рис. 7. Временная диаграмма работы комплементарного инвертора

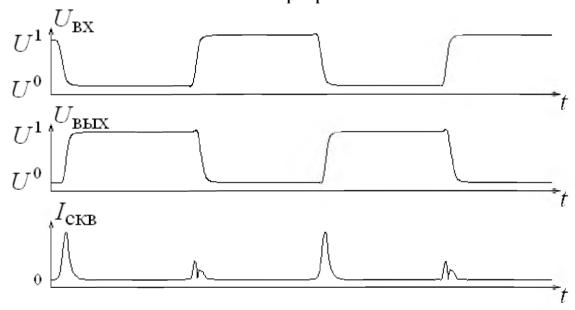

Два варианта топологии комплементарного инвертора показаны на рис. 8. Как правило, при одинаковой длине затвора ширина затвора МОП-транзистора с индуцированным каналом р-типа больше ширины затвора МОП-транзистора с индуцированным каналом *п*поэтому размещение транзисторов согласно рис. 8, a не типа, обеспечивает компактность топологии и требует на кристалле избыточной площади. При этом часть площади кристалла (правый нижний УГОЛ топологии) оказывается не занятой никакими элементами. Таким образом, использование топологии рис. 8, а не представляется разумным.

Рис. 8. Топологии комплементарного инвертора

В большинстве случаев применяют топологию комплементарного инвертора, представленную на рис. 8, 6. Затворы транзисторов выполняются с помощью слоя поликремния, который и МОП-транзистора используют ДЛЯ соединения затворов МОП-транзистора индуцированным каналом р-типа И индуцированным каналом *п*-типа. Для подключения инвертора к другим элементам схемы чаще всего переходят на первый слой металла, поэтому входным узлом «in» является переходной контакт между слоем поликремния и первым слоем металла. Стоки и истоки транзисторов имеют выводы на первый слой металла, поэтому выходным узлом «out» является соединение первым слоем металла стоков МОП-транзистора с индуцированным каналом p-типа и МОПтранзистора с индуцированным каналом *п*-типа. Исток МОПтранзистора с индуцированным каналом р-типа подключается первым слоем металла к шине питания  $E_{\text{пит}}$ , которая на рис. 8 обозначена «vdd» и представлена контактом на подложку области *n*-типа, в которой расположен МОП-транзистор с индуцированным каналом р-Исток МОП-транзистора с каналом *п*-типа подключается первым слоем металла к земляному узлу, который на рис. 8 обозначен «gnd» и представлен контактом на подложку области *p*-типа.

#### 2.2. ЛОГИЧЕСКИЕ ФУНКЦИИ И АЛГЕБРА ЛОГИКИ

У комбинационных цифровых схем [2–10] состояние выхода однозначно определяется набором входных сигналов. Комплементарный инвертор выполняет простейшую бинарную логическую операцию — отрицание, являясь схемной реализацией элемента с логической функцией «НЕ»  $Y = \overline{X}$ , где X — входная, а Y — выходная логические переменные (рис. 5,  $\delta$ ), принимающие значения из множества  $\{0,1\}$ . Таблица истинности представлена в табл. 1.

Таблица 1

## Таблица истинности логической функции «НЕ»

| X | $Y = \overline{X}$ |

|---|--------------------|

| 0 | 1                  |

| 1 | 0                  |

Распространёнными логическими функциями являются: «И» – конъюнкция

$$Y = X_1 \wedge X_2 = X_1 \cdot X_2$$

;

«И-НЕ» – отрицание конъюнкции, штрих Шеффера

$$Y = \overline{X_1 \wedge X_2} = \overline{X_1 \cdot X_2} \; ;$$

«ИЛИ» – дизъюнкция

$$Y = X_1 \lor X_2 = X_1 + X_2$$

;

«ИЛИ-НЕ» – отрицание дизъюнкции, стрелка Пирса

$$Y = \overline{X_1 \vee X_2} = \overline{X_1 + X_2} \; ;$$

«исключающее ИЛИ»

$$Y = X_1 \oplus X_2;$$

«И-ИЛИ-НЕ»

$$Y = \overline{X_1 \cdot X_2 + X_3 \cdot X_4};$$

«ИЛИ-И-НЕ»

$$Y = \overline{(X_1 + X_2) \cdot (X_3 + X_4)};$$

мультиплексирование

$$Y = X_1 \cdot X_2 + \overline{X_1} \cdot X_3.$$

Каждая из указанных функций может быть распространена на 16

большее число логических переменных. Таблицы истинности представлены в табл. 2, 3 и 4. Система логических функций является функционально полной, если с помощью суперпозиции входящих в неё функций возможно получить любую логическую функцию. Известны пять функционально полных систем:

- 1) «HE», «И», «ИЛИ»;

- 2) «HE», «И»;

- 3) «HE», «ИЛИ»;

- 4) «И-HE»;

- **5)** «ИЛИ-НЕ».

Каждая из указанных систем может быть реализована на основе логических элементов. Недостающие в этих системах логические функции можно получить на основе известных аксиом (тождеств) и правил (законов) алгебры логики:

- 1)  $\overline{\overline{X}} = X$ ;

- 2)  $X \cdot X = X$ , X + X = X,  $X \oplus X = 0$ ;

- 3)  $X \cdot \overline{X} = 0$ ,  $X + \overline{X} = 1$ ,  $X \oplus \overline{X} = 1$ ;

- 4)  $X \cdot 0 = 0, X + 0 = X, X \oplus 0 = X;$

- 5)  $X \cdot 1 = X, X + 1 = 1, X \oplus 1 = \overline{X};$

- 6)  $X_1 \cdot X_2 = X_2 \cdot X_1, X_1 + X_2 = X_2 + X_1, X_1 \oplus X_2 = X_2 \oplus X_1;$

- 7)  $X_1 \cdot (X_2 \cdot X_3) = (X_1 \cdot X_2) \cdot X_3,$   $X_1 + (X_2 + X_3) = (X_1 + X_2) + X_3,$  $X_1 \oplus (X_2 \oplus X_3) = (X_1 \oplus X_2) \oplus X_3;$

- 8)  $X_1 \cdot (X_2 + X_3) = X_1 \cdot X_2 + X_1 \cdot X_3,$   $X_1 + (X_2 \cdot X_3) = (X_1 + X_2) \cdot (X_1 + X_3),$  $X_1 \cdot (X_2 \oplus X_3) = (X_1 \oplus X_2) \cdot (X_1 \oplus X_3);$

- 9)  $\overline{X_1 \cdot X_2} = \overline{X_1} + \overline{X_2}, \ \overline{X_1 + X_2} = \overline{X_1} \cdot \overline{X_2},$  $\overline{X_1 \oplus X_2} = X_1 \oplus \overline{X_2} = \overline{X_1} \oplus X_2;$

- 10)  $X_1 \cdot X_2 + X_1 \cdot \overline{X_2} = X_1$ ,  $(X_1 + X_2) \cdot (X_1 + \overline{X_2}) = X_1$ ;

- 11)  $X_1 \cdot (X_1 + X_2) = X_1, X_1 + (X_1 \cdot X_2) = X_1;$

- 12)  $X_1 \oplus X_2 = X_1 \cdot \overline{X_2} + \overline{X_1} \cdot X_2 = (X_1 + X_2) \cdot (\overline{X_1} + \overline{X_2})$ .

Таблица 2 **Таблицы истинности логических функций «И», «И-НЕ», «ИЛИ»,** «ИЛИ-НЕ», «исключающее ИЛИ» и «исключающее ИЛИ-НЕ»

| V     | V     | Y =             |                            |             |                        |                  |                             |  |  |  |

|-------|-------|-----------------|----------------------------|-------------|------------------------|------------------|-----------------------------|--|--|--|

| $A_1$ | $X_2$ | $X_1 \cdot X_2$ | $\overline{X_1 \cdot X_2}$ | $X_1 + X_2$ | $\overline{X_1 + X_2}$ | $X_1 \oplus X_2$ | $\overline{X_1 \oplus X_2}$ |  |  |  |

| 0     | 0     | 0               | 1                          | 0           | 1                      | 0                | 1                           |  |  |  |

| 0     | 1     | 0               | 1                          | 1           | 0                      | 1                | 0                           |  |  |  |

| 1     | 0     | 0               | 1                          | 1           | 0                      | 1                | 0                           |  |  |  |

| 1     | 1     | 1               | 0                          | 1           | 0                      | 0                | 1                           |  |  |  |

Таблица 3 **Таблица истинности логических функций**«И-ИЛИ-НЕ» и «ИЛИ-И-НЕ»

| $X_1$ | $X_2$ | $X_3$ | $X_4$ | $Y = \overline{X_1 \cdot X_2 + X_3 \cdot X_4}$ | $Y = \overline{(X_1 + X_2) \cdot (X_3 + X_4)}$ |

|-------|-------|-------|-------|------------------------------------------------|------------------------------------------------|

| 0     | 0     | 0     | 0     | 1                                              | 1                                              |

| 0     | 0     | 0     | 1     | 1                                              | 1                                              |

| 0     | 0     | 1     | 0     | 1                                              | 1                                              |

| 0     | 0     | 1     | 1     | 0                                              | 1                                              |

| 0     | 1     | 0     | 0     | 1                                              | 1                                              |

| 0     | 1     | 0     | 1     | 1                                              | 0                                              |

| 0     | 1     | 1     | 0     | 1                                              | 0                                              |

| 0     | 1     | 1     | 1     | 0                                              | 0                                              |

| 1     | 0     | 0     | 0     | 1                                              | 1                                              |

| 1     | 0     | 0     | 1     | 1                                              | 0                                              |

| 1     | 0     | 1     | 0     | 1                                              | 0                                              |

| 1     | 0     | 1     | 1     | 0                                              | 0                                              |

| 1     | 1     | 0     | 0     | 0                                              | 1                                              |

| 1     | 1     | 0     | 1     | 0                                              | 0                                              |

| 1     | 1     | 1     | 0     | 0                                              | 0                                              |

| 1     | 1     | 1     | 1     | 0                                              | 0                                              |

Таблица 4

Таблица истинности логической функции мультиплексора

| $X_1$ | $X_2$ | $X_3$ | $Y = X_1 \cdot X_2 + \overline{X_1} \cdot X_3$ | $\overline{Y} = \overline{X_1 \cdot X_2 + \overline{X_1} \cdot X_3}$ |

|-------|-------|-------|------------------------------------------------|----------------------------------------------------------------------|

| 0     | 0     | 0     | 0                                              | 1                                                                    |

| 0     | 0     | 1     | 1                                              | 0                                                                    |

| 0     | 1     | 0     | 0                                              | 1                                                                    |

| 0     | 1     | 1     | 1                                              | 0                                                                    |

| 1     | 0     | 0     | 0                                              | 1                                                                    |

| 1     | 0     | 1     | 0                                              | 1                                                                    |

| 1     | 1     | 0     | 1                                              | 0                                                                    |

| 1     | 1     | 1     | 1                                              | 0                                                                    |

#### 2.3. ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ «И-НЕ» И «ИЛИ-НЕ»

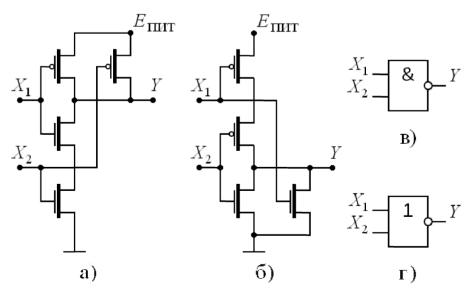

Схемы логических элементов «И-НЕ» и «ИЛИ-НЕ» [1, 2, 8, 10] на комплементарных транзисторах показаны на рис. 9, a и рис. 9, b, а условные обозначения — на рис. 9, b и рис. 9, b соответственно. Здесь и в остальных схемах выводы подложки не показаны, подразумевается, что все подложки МОП-транзисторов с индуцированным каналом b-типа соединены с земляным узлом, а подложки МОП-транзисторов с индуцированным каналом b-типа соединены с узлом b-типа соединена с узлом b

Рис. 9. Элементы «И-НЕ» и «ИЛИ-НЕ»

По принципу действия данные схемы аналогичны комплементарному инвертору (рис. 5, a). Отличительной рис. 9 является наличие особенностью схем параллельных последовательных соединений транзисторов. Причём параллельное соединение одного типа транзисторов используется совместно с последовательным соединением транзисторов другого типа. Вид сигналов в схемах «И-НЕ» и «ИЛИ-НЕ» во временной области представлен на рис. 10.

Рис. 10. Временные диаграммы работы элементов «И-НЕ» и «ИЛИ-НЕ»

В схеме логического элемента «И-НЕ» (рис. 9, a) транзисторы с каналом n-типа включены последовательно, а транзисторы с каналом

р-типа – параллельно. Пусть хотя бы на один из входов схемы подано напряжение логического нуля  $U_{\rm Bx} = U^0 < U_{\rm O} n$ , тогда хотя бы один из транзисторов с каналом n-типа закрыт, и ток через последовательное соединение этих транзисторов определяется лишь утечкой. При этом, поскольку  $U^0 - E_{\text{пит}} < U_{\text{о}\,p}$  , то хотя бы один из транзисторов с каналом р-типа открыт и пропускает ток заряда ёмкости нагрузки, и  $U_{\scriptscriptstyle

m Bbix}\cong E_{\scriptscriptstyle

m IIIII}=U^1$  . Только в том случае если одновременно на оба входа подано напряжение логической единицы  $U_{\mathrm{BX}} = U^1 > U_{\mathrm{o}\,n}$  , тогда оба транзистора с каналом *n*-типа открыты, и через последовательное соединение этих транзисторов протекает ток разряда ёмкости нагрузки  $U_{\text{вых}} \cong 0 = U^0$ . При этом, поскольку  $U^1 - E_{\text{пит}} > U_{\text{о }p}$  , то оба транзистора с каналом р-типа закрыты, и ток через них работа лишь определяется утечкой. Такая схемы рис. 9, а соответствует таблице истинности логической функции «И-НЕ», представленной в табл. 2.

B элемента «ИЛИ-НЕ» (puc.  $9, \delta$ ) схеме логического транзисторы с каналом *п*-типа включены параллельно, а транзисторы с каналом р-типа – последовательно. Пусть хотя бы на один из входов схемы подано напряжение логической единицы  $U_{\rm BX} = U^1 > U_{{

m o}\,n}$  , тогда хотя бы один из транзисторов с каналом п-типа открыт и пропускает ток разряда ёмкости нагрузки  $U_{\text{вых}} \cong 0 = U^0$ . При этом, поскольку  $U^1 - E_{\text{пит}} > U_{\text{о}\,p}$  , то хотя бы один из транзисторов с каналом p-типа закрыт, и ток через последовательное соединение этих транзисторов определяется лишь утечкой. Только в том случае если одновременно на оба входа подано напряжение логического нуля  $U_{\scriptscriptstyle \mathrm{BX}} = U^0 < U_{\scriptscriptstyle \mathrm{O}} n$  , тогда оба транзистора с каналом n-типа закрыты, и ток через них определяется лишь утечкой. При этом, поскольку  $U^0 - E_{\text{пит}} < U_{\text{о}\,p}$  , то оба транзистора с каналом p-типа открыты, и через последовательное соединение этих транзисторов протекает ток заряда ёмкости нагрузки  $U_{\text{вых}} \cong E_{\text{пит}} = U^1$ . Такая работа схемы рис. 9,  $\delta$  соответствует таблице истинности логической функции «ИЛИ-НЕ», представленной в табл. 2.

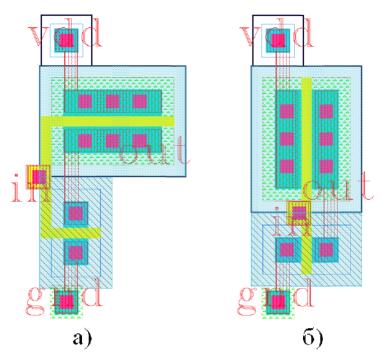

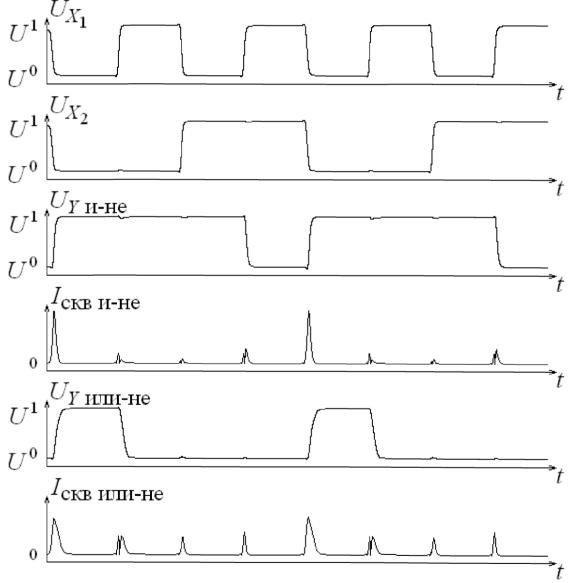

Топологии элементов «И-НЕ» рис. 9, a и «ИЛИ-НЕ» рис. 9,  $\delta$ показаны на рис. 11, a и рис. 11,  $\delta$ , соответственно. Затворы МОПтранзисторов соединены с помощью слоя поликремния. подключения к другим элементам схемы входными узлами «in1» и «in2» являются переходные контакты между слоем поликремния и первым слоем металла. Соединения стоков МОП-транзисторов с индуцированным каналом *p*-типа в элементе «И-НЕ» и стоков МОПтранзисторов с индуцированным каналом *n*-типа в элементе «ИЛИ-НЕ» выполнены вторым слоем металла. Выходным узлом «out» является соединение первым МОПслоем металла стоков транзисторов с индуцированными каналами р-типа и п-типа. Первым слоем металла выполнено подключение к шине питания  $E_{\text{пит}}$ , обозначенной «vdd» и представленной контактом на подложку в которой расположены МОП-транзисторы с области *п*-типа, индуцированным каналом р-типа. Первым слоем металла выполнено подключение К земляному узлу, обозначенному «gnd» представленному контактом на подложку области р-типа.

Рис. 11. Топологии «И-НЕ» и «ИЛИ-НЕ»

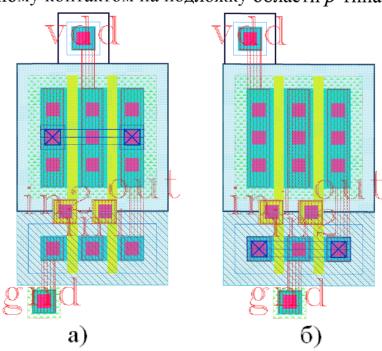

При необходимости использования логических элементов «И-НЕ» и «ИЛИ-НЕ» с большим числом входов в схемы рис. 9 как в параллельное, так и в последовательное соединение включаются дополнительные транзисторы. Число транзисторов с каналом *п*-типа равно числу транзисторов с каналом *p*-типа и равно числу входов. В рамках такого подхода возможно получить логические элементы «И-НЕ» и «ИЛИ-НЕ» с числом входов не более четырёх. Схемы логических элементов «И-НЕ» и «ИЛИ-НЕ» с четырьмя входами показаны на рис. 12, *a* и рис. 12, *б* соответственно.

Рис. 12. Элементы «И-НЕ» и «ИЛИ-НЕ» с четырьмя входами

#### 2.4. ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ «И-ИЛИ-НЕ» И «ИЛИ-И-НЕ»

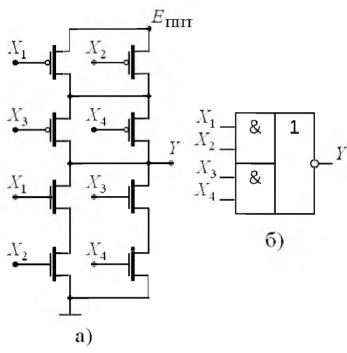

Схема логического элемента «И-ИЛИ-НЕ» на комплементарных транзисторах [2, 8, 10] показана на рис. 13, a, а условное обозначение — на рис. 13,  $\delta$ . Как и в случае схем на рис. 9, в данном случае используются параллельные и последовательные соединения

транзисторов. Причём при одноименных входных сигналах параллельное соединение одного типа транзисторов используется совместно с последовательным соединением транзисторов другого типа.

Рис. 13. Элемент «И-ИЛИ-НЕ»

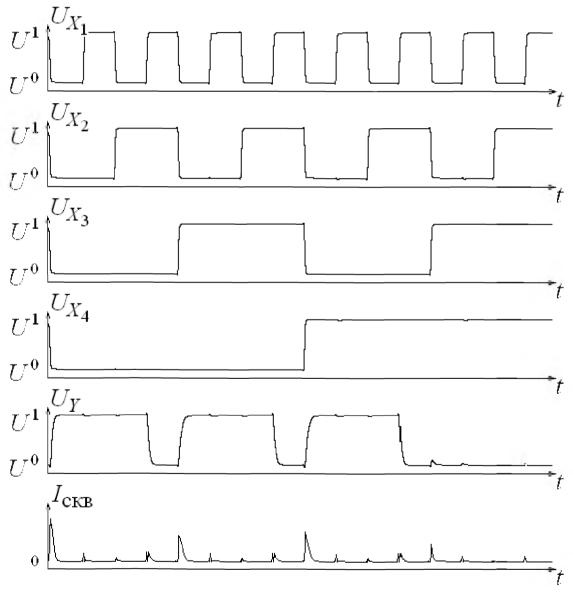

Пусть одновременно хотя бы на один из входов  $X_1$  либо  $X_2$  и один из входов  $X_3$  либо  $X_4$  схемы рис. 13, a подано напряжение логического нуля  $U_{\mathrm{Bx}} = U^0 < U_{\mathrm{O}n}$  , тогда транзисторы с каналом nтипа, на затворы которых поступают напряжения логического нуля, закрыты, и ток через обе цепи последовательных соединений транзисторов с каналом *п*-типа определяется лишь утечкой. При этом, поскольку  $U^0 - E_{\text{пит}} < U_{\text{о} p}$ , каждом И3 параллельных соединений транзисторов с каналом р-типа открыт, по крайней мере, ИЗ транзисторов, и через последовательное соединение ОДИН открытых транзисторов с каналом p-типа протекает ток заряда ёмкости нагрузки, и  $U_{\text{вых}} \cong E_{\text{пит}} = U^1$ . Только в том случае если хотя бы на одну из пар входов либо  $X_1$  и  $X_2$ , либо  $X_3$  и  $X_4$  одновременно подано напряжение логической единицы  $U_{\mathrm{Bx}} = U^{\mathrm{I}} > U_{\mathrm{o}\,n}$  , тогда хотя бы одно из последовательных соединений транзисторов с каналом n-типа открыто и пропускает ток разряда ёмкости нагрузки  $U_{\text{вых}} \cong 0 = U^0$ . При этом, поскольку  $U^1 - E_{\text{пит}} > U_{\text{о}\,p}$ , то хотя бы в одном из параллельных соединений транзисторов с каналом p-типа закрыты сразу оба транзистора и ток через них определяется лишь утечкой. Такая работа схемы рис. 13, a соответствует таблице истинности логической функции «И-ИЛИ-НЕ», представленной в табл. 3. Вид сигналов схемы «И-ИЛИ-НЕ» во временной области представлен на рис. 14.

Рис. 14. Временные диаграммы работы элемента «И-ИЛИ-НЕ»

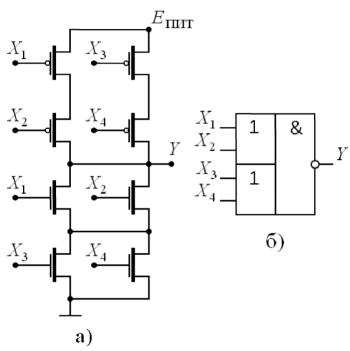

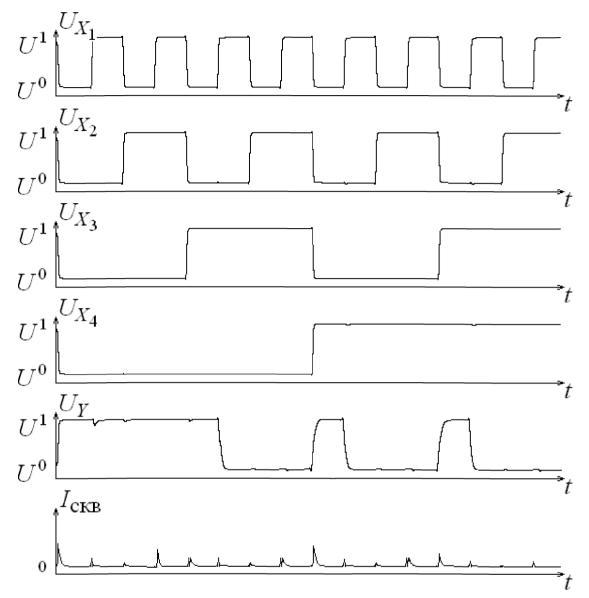

Схема логического элемента «ИЛИ-И-НЕ» на комплементарных транзисторах [2, 8, 10] показана на рис. 15, *a*, а условное обозначение — на рис. 15, *б*. В схеме используются параллельные и последовательные соединения транзисторов. Причём параллельное соединение одного типа транзисторов используется совместно с последовательным соединением транзисторов другого типа при одноименных входных сигналах. Вид сигналов схемы «ИЛИ-И-НЕ» во временной области представлен на рис. 16.

Рис. 15. Элемент «ИЛИ-И-НЕ»

#### 2.5. МУЛЬТИПЛЕКСОРЫ

Анализ материалов публикаций позволяет утверждать, что за рубежом проявляется интерес к схемам, получившим название «passtransistor logic» [2, 4]. Главное отличие данных схем OT рассмотренных в предыдущих пунктах заключается в том, входные сигналы подаются не только на затворы, но и на стоки или истоки транзисторов. Такие цепи можно назвать логическими схемами на проходных транзисторах, ИЛИ на транзисторах с дополнительным управлением по стоку или истоку.

Рис. 16. Временные диаграммы работы элемента «ИЛИ-И-НЕ»

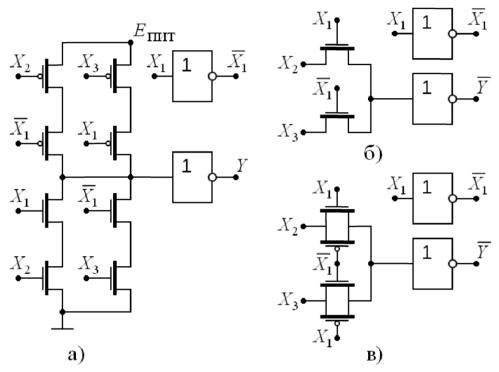

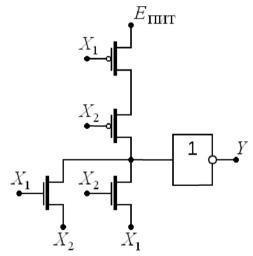

На рис. 17 представлены схемные решения двухвходового мультиплексора. Схема с управлением только по затвору показана на рис. 17, a, а с дополнительным управлением по стоку или истоку — на рис. 17,  $\delta$  и рис. 17,  $\epsilon$ . Мультиплексор имеет адресный вход  $X_1$  (используются как прямые  $X_1$ , так и инверсные сигналы адреса  $\overline{X_1}$ ), входы данных, обозначенные  $X_2$  и  $X_3$ , выход Y либо  $\overline{Y}$ .

В схемах с дополнительным управлением по стоку или истоку (рис. 17,  $\delta$  и рис. 17,  $\epsilon$ ) адресные сигналы подаются на затворы транзисторов, а входами данных служат стоки или истоки транзисторов. При воздействии напряжением логической единицы  $U^1$

на вход  $X_1$  на выходе Y формируется логическое состояние, соответствующее  $X_2$ , а на выходе  $\overline{Y}$  — соответственно инвертированное  $\overline{X_2}$ . При воздействии напряжением логического нуля на вход  $X_1$  на выходе Y формируется логическое состояние, соответствующее  $X_3$ , а на выходе  $\overline{Y}$  — будет  $\overline{X_3}$ .

Рис. 17. Двухвходовые мультиплексоры

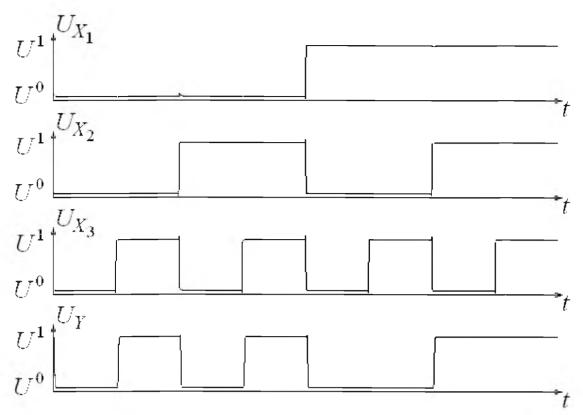

временной области Вид сигналов в схемах рис. 17 во представлен на рис. 18. Исходя из рис. 17, очевидным преимуществом мультиплексора транзисторах схем двухвходового на дополнительным управлением по стоку или истоку (рис. 17, б и рис. 17,  $\epsilon$ ) по сравнению со схемой с управлением только по затвору (рис. 17, a) является меньшее число транзисторов. Данное обстоятельство позволяет добиться экономии площади, занимаемой схемой, за счёт компактного расположения транзисторов уменьшения длины соединительных проводников в слоях металлов.

Рис. 18. Временные диаграммы работы мультиплексора

# 2.6. ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ «ИСКЛЮЧАЮЩЕЕ ИЛИ» И «ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ»

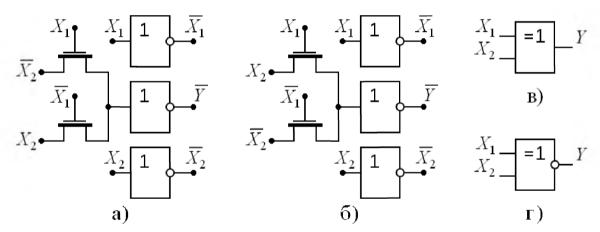

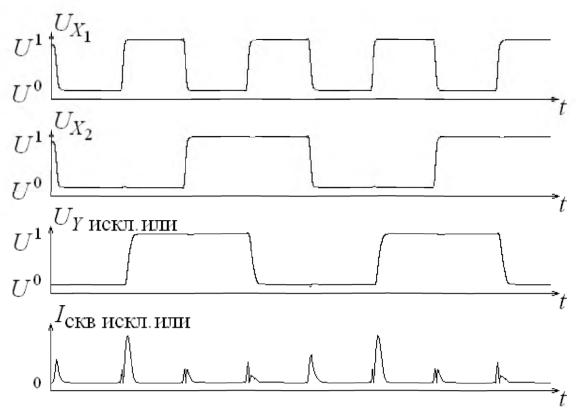

При синтезе цифровых устройств на основе схем на транзисторах с управлением только по затвору в качестве базисных логических элементов используют реализации функции «И-НЕ» и «ИЛИ-НЕ», аналогичные рис. 9. Цифровые устройства с применением схем на транзисторах с дополнительным управлением по стоку или истоку ориентированы на логические функции «исключающее ИЛИ» (рис. 19, a) либо «исключающее ИЛИ-НЕ» (рис. 19,  $\delta$ ) Представленные на рис. 19 схемы являются частным случаем мультиплексоров, рассмотренных в предыдущем пункте. Условные на рис. 19, в обозначения элементов приведены соответственно, а вид сигналов во временной области на рис. 20.

К недостаткам схем на транзисторах с дополнительным управлением по стоку или истоку можно отнести следующее:

- логический перепад сигнала на входе инверторов (рис. 19)

уменьшен на величину порогового напряжения отпирания вследствие падения напряжения на проходных транзисторах с каналом *n*-типа, представляющих входные цепи:  $U_{\rm л} = E_{\rm пит} - U_{\rm o} n$ . Поэтому на выходе этих схем для обеспечения логического перепада сигнала близкого по величине напряжению питания необходимо использовать транзисторах. Кроме инверторы на комплементарных τογο, включение инверторов на выходе элементов позволяет обеспечивать способность нагрузочную по выходу при увеличении нагрузки  $C_{\tt u}$ ;

– в схемах используются не только прямые, но и инверсные входные сигналы, наличие которых обеспечивается, например, с помощью дополнительных инверторов на комплементарных транзисторах.

Рис. 19. Элементы «исключающее ИЛИ» и «исключающее ИЛИ-НЕ»

Схема «исключающее ИЛИ» рис. 21 позволяет избавиться от необходимости инверсных входных сигналов. На транзисторы с каналом р-типа входные сигналы подаются только на затворы, в то время как ДЛЯ транзисторов C каналом *п*-типа используется дополнительное управление по стоку или истоку. Для восстановления выходе поставлен инвертор логического перепада на комплементарных транзисторах. Вид сигналов во временной области аналогичен рис. 20.

Рис. 20. Временные диаграммы работы элемента «исключающее ИЛИ»

Рис. 21. Элемент «исключающее ИЛИ»

## 2.7. СИНТЕЗ КОМБИНАЦИОННЫХ ЦИФРОВЫХ СХЕМ

# 2.7.1. СОВЕРШЕННЫЕ ДИЗЪЮНКТИВНАЯ И КОНЪЮНКТИВНАЯ НОРМАЛЬНЫЕ ФОРМЫ

Традиционные методы синтеза комбинационных цифровых схем на основе конъюнктивной и дизъюнктивной нормальной форм,

минимизации выражений логических функций с использованием метода Куайна и карт Карно рассмотрены в монографиях [3, 5–7, 9].

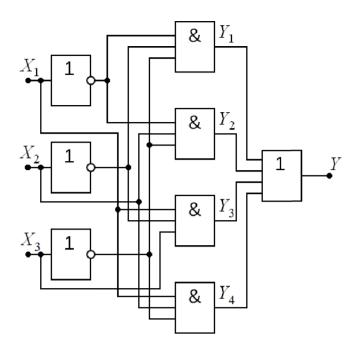

Существуют два основных способа записи выражения логической функции либо в виде совершенной дизъюнктивной нормальной формы (СДНФ), либо совершенной В виде конъюнктивной нормальной формы (СКНФ). Рассмотрим переход от таблицы истинности к логической функции в виде СДНФ. Таблица истинности для логической функции У с тремя входными сигналами  $X_1$ ,  $X_2$  и  $X_3$  представлена в табл. 5 первыми четырьмя столбцами. Введём четыре вспомогательных функции  $Y_1$ ,  $Y_2$ ,  $Y_3$  и  $Y_4$  по числу единиц в столбце искомой функции У, т.е.:

$$Y = Y_1 + Y_2 + Y_3 + Y_4.$$

Таблица 5 **Таблица истинности логической функции**

| $X_1$ | $X_2$ | $X_3$ | Y | <i>Y</i> <sub>1</sub> | <i>Y</i> <sub>2</sub> | <i>Y</i> <sub>3</sub> | $Y_4$ | <i>Y</i> <sub>5</sub> | <i>Y</i> <sub>6</sub> | <i>Y</i> <sub>7</sub> | <i>Y</i> <sub>8</sub> |

|-------|-------|-------|---|-----------------------|-----------------------|-----------------------|-------|-----------------------|-----------------------|-----------------------|-----------------------|

| 0     | 0     | 0     | 1 | 1                     | 0                     | 0                     | 0     | 1                     | 1                     | 1                     | 1                     |

| 0     | 0     | 1     | 0 | 0                     | 0                     | 0                     | 0     | 0                     | 1                     | 1                     | 1                     |

| 0     | 1     | 0     | 1 | 0                     | 1                     | 0                     | 0     | 1                     | 1                     | 1                     | 1                     |

| 0     | 1     | 1     | 0 | 0                     | 0                     | 0                     | 0     | 1                     | 0                     | 1                     | 1                     |

| 1     | 0     | 0     | 0 | 0                     | 0                     | 0                     | 0     | 1                     | 1                     | 0                     | 1                     |

| 1     | 0     | 1     | 1 | 0                     | 0                     | 1                     | 0     | 1                     | 1                     | 1                     | 1                     |

| 1     | 1     | 0     | 1 | 0                     | 0                     | 0                     | 1     | 1                     | 1                     | 1                     | 1                     |

| 1     | 1     | 1     | 0 | 0                     | 0                     | 0                     | 0     | 1                     | 1                     | 1                     | 0                     |

По табл. 5 составим формулы для вспомогательных функций, описывая логические единицы логическими произведениями трёх входных сигналов в соответствующей строке:

$$Y_1=\overline{X_1}\cdot\overline{X_2}\cdot\overline{X_3}\,;\;Y_2=\overline{X_1}\cdot X_2\cdot\overline{X_3}\,;\;Y_3=X_1\cdot\overline{X_2}\cdot X_3;\;Y_4=X_1\cdot X_2\cdot\overline{X_3}\,.$$

Тогда выражение для логической функции Y в виде СДН $\Phi$  следующее:

$$Y = \overline{X_1} \cdot \overline{X_2} \cdot \overline{X_3} + \overline{X_1} \cdot X_2 \cdot \overline{X_3} + X_1 \cdot \overline{X_2} \cdot X_3 + X_1 \cdot X_2 \cdot \overline{X_3}.$$

Схема на логических элементах «НЕ», «И» и «ИЛИ» показана на рис. 22.

Рис. 22. Схемная реализация функции в СДНФ

Таким образом, логическая функция имеет единственное представление в виде СДНФ: входящие в логическую сумму логические произведения содержат все входные сигналы, и каждый из них входит только один раз в прямом или инверсном виде. При этом в СДНФ нет двух одинаковых произведений, и ни одно из произведений не содержит двух одинаковых множителей либо множитель и его инверсию.

Рассмотрим на примере переход от таблицы истинности к логической функции в виде СКНФ. Таблица истинности представлена в табл. 5. Введём четыре вспомогательных функции  $Y_5$ ,  $Y_6$ ,  $Y_7$  и  $Y_8$  по числу нулей в столбце искомой логической функции Y, т.е.:

$$Y = Y_5 \cdot Y_6 \cdot Y_7 \cdot Y_8.$$

По табл. 5 составим формулы для вспомогательных функций, описывая логические нули логическими суммами трёх входных сигналов в соответствующей строке:

$$Y_5 = X_1 + X_2 + \overline{X_3}; Y_6 = X_1 + \overline{X_2} + \overline{X_3};$$

$Y_7 = \overline{X_1} + X_2 + X_3; Y_8 = \overline{X_1} + \overline{X_2} + \overline{X_3}.$

Тогда выражение для логической функции Y в виде СКНФ следующее:

$$Y = (X_1 + X_2 + \overline{X_3}) \cdot (X_1 + \overline{X_2} + \overline{X_3}) \cdot (\overline{X_1} + X_2 + X_3) \cdot (\overline{X_1} + \overline{X_2} + \overline{X_3}).$$

Схема на логических элементах «НЕ», «ИЛИ» и «И» показана на рис. 23.

Таким образом, логическая функция имеет единственное представление в виде СКНФ: входящие в логическое произведение логические суммы содержат все входные сигналы, и каждый из них входит только один раз в прямом или инверсном виде. При этом в СКНФ нет двух одинаковых сумм, ни одна из сумм не содержит двух одинаковых слагаемых либо слагаемое и его инверсию.

Рис. 23. Схемная реализация функции в СКНФ

Применение известных аксиом (тождеств) и правил (законов) алгебры логики даёт возможность, производя эквивалентные преобразования, упрощать СДНФ и СКНФ логических функций, т.е. находить для них более простые выражения. Так, для полученной ранее СДНФ, выполнив эквивалентные преобразования, имеем:

$$Y = \overline{X_1} \cdot (\overline{X_2} + X_2) \cdot \overline{X_3} + (\overline{X_1} + X_1) \cdot X_2 \cdot \overline{X_3} + X_1 \cdot \overline{X_2} \cdot X_3 =$$

$$= \overline{X_1} \cdot \overline{X_3} + X_2 \cdot \overline{X_3} + X_1 \cdot \overline{X_2} \cdot X_3.$$

Для полученной ранее СКНФ, выполнив эквивалентные преобразования, имеем:

$$Y = (X_1 + X_2 \cdot \overline{X_2} + \overline{X_3}) \cdot (X_1 \cdot \overline{X_1} + \overline{X_2} + \overline{X_3}) \cdot (\overline{X_1} + X_2 + X_3) =$$

$$= (X_1 + \overline{X_3}) \cdot (\overline{X_2} + \overline{X_3}) \cdot (\overline{X_1} + X_2 + X_3).$$

## 2.7.2. МЕТОД КУАЙНА

Как правило, для эквивалентных преобразований СДНФ и СКНФ используются операции склеивания и поглощения (стр. 17, операции 10 и 11). Данные преобразования лежат в основе минимизации выражений логических функций по методу Куайна [3]. Операция склеивания логической суммы логических произведений выполняется, если в этих произведениях есть одинаковый первый множитель, а второй множитель в одно произведение входит в прямом виде, а в другое — в инверсном. В результате операции склеивания остаётся лишь одинаковый первый множитель:

$$X_1 \cdot X_2 + X_1 \cdot \overline{X_2} = X_1 \cdot (X_2 + \overline{X_2}) = X_1.$$

Если первое из двух слагаемых имеет вид множителя в составе второго слагаемого, выполняется операция поглощения, в результате которой остаётся лишь первое слагаемое:

$$X_1 + X_1 \cdot X_2 = X_1 \cdot (1 + X_2) = X_1$$

.

Операция склеивания логического произведения логических сумм выполняется, если в этих суммах есть одинаковое первое слагаемое, а второе слагаемое в одну сумму входит в прямом виде, а в другую – в инверсном. В результате операции склеивания остаётся лишь одинаковое первое слагаемое:

$$(X_1 + X_2) \cdot (X_1 + \overline{X_2}) = X_1 + X_1 \cdot (X_2 + \overline{X_2}) + X_2 \cdot \overline{X_2} = X_1.$$

Если первый из двух множителей имеет вид слагаемого в составе второго множителя, то выполняется операция поглощения, в результате которой остаётся лишь первый множитель:

$$X_1 \cdot (X_1 + X_2) = X_1 + X_1 \cdot X_2 = X_1 \cdot (1 + X_2) = X_1$$

.

В случае применения метода Куайна для минимизации выражения логической функции, с увеличением числа входных сигналов возрастает число логических произведений и сумм и, соответственно, число анализируемых вариантов склеиваний и поглощений, что является очевидным недостатком. Кроме того, в результате склеивания могут появляться лишние слагаемые или сомножители.

#### **2.7.3. КАРТЫ КАРНО**

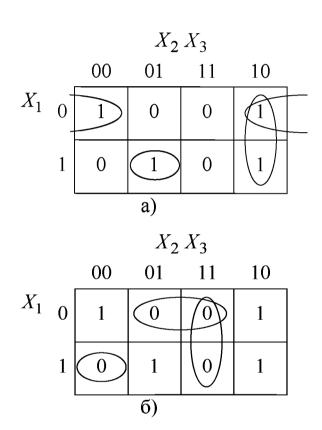

При минимизации выражений логических функций на основе карт Карно [3] используются те же операции, что и при минимизации по методу Куайна, но формой представления исходных данных является карта с числом клеток  $2^{N}$ , где N — число входных сигналов искомой логической функции. Кодировка клеток карты Карно определяется значениями входных сигналов, при этом коды клеток карты заданы в коде Грея, т.е. соседние клетки отличаются значениями только одного из входных сигналов. То есть клетка карты Карно соответствует строке таблицы истинности и заполняется логической функции В данной строке. значением Признаком выполнения операции склеивания является расположение в соседних клетках одинаковых логических значений. Отметим, что соседними друг другу считаются и крайние по вертикали в соответствующем столбце, и крайние по горизонтали в соответствующей строке клетки.

На рис. 24 показана карта Карно для логической функции У, таблица истинности которой представлена в табл. 5. Для получения минимизированного выражения логической функции в виде суммы произведений рис. 24, а операции на склеивания показаны замкнутыми контурами, охватывающими соседние логические Каждый представляется единицы. ИЗ полученных контуров логическим произведением не изменяющихся в рамках контура входных сигналов (кодов клеток карты), причём входной сигнал, кодируемый логической единицей, входит в произведение в прямом виде, а кодируемый логическим нулём – в обратном. Не входящая в контуры логическая единица представляется логическим произведением всех входных сигналов в прямом или обратном виде согласно коду клетки карты. Таким образом, получим:

$$Y = \overline{X_1} \cdot \overline{X_3} + X_2 \cdot \overline{X_3} + X_1 \cdot \overline{X_2} \cdot X_3.$$

Для получения минимизированного выражения логической функции в виде произведения сумм на рис. 24, б операции склеивания показаны замкнутыми контурами, охватывающими соседние логические нули. Каждый из полученных контуров представляется

логической суммой не изменяющихся в рамках контура входных сигналов (кодов клеток карты), причём входной сигнал, кодируемый логическим нулём, входит в сумму в прямом виде, а кодируемый логической единицей — в обратном. Не входящий в контуры логический ноль представляется логической суммой всех входных сигналов в прямом или обратном виде согласно коду клетки карты. Таким образом, получим:

$$Y = (X_1 + \overline{X_3}) \cdot (\overline{X_2} + \overline{X_3}) \cdot (\overline{X_1} + X_2 + X_3).$$

Рис. 24. Карта Карно логической функции из табл. 5.

В общем случае в результате операций склеивания в картах Карно образуются контуры, охватывающие  $2^n$  клеток, где n=1,2,...,N. На рис. 25 показана карта Карно для логической функции «И-ИЛИ-НЕ», таблица истинности которой представлена в табл. 3. Минимизированное выражение логической функции в виде суммы произведений согласно рис. 25, a имеет вид:

$$Y = \overline{X_1} \cdot \overline{X_3} + \overline{X_1} \cdot \overline{X_4} + \overline{X_2} \cdot \overline{X_3} + \overline{X_2} \cdot \overline{X_4}$$

Минимизированное выражение функции «И-ИЛИ-НЕ» в виде произведения сумм согласно рис. 25, б имеет более компактный вид:

$$Y = (\overline{X_1} + \overline{X_2}) \cdot (\overline{X_3} + \overline{X_4}).$$

Для получения выражения логической функции «И-ИЛИ-НЕ» из табл. 3 воспользуемся законом двойного отрицания, т.е.:

$$Y = \overline{\overline{Y}} = \overline{(\overline{X_1} + \overline{X_2}) \cdot (\overline{X_3} + \overline{X_4})} = \overline{(\overline{X_1} + \overline{X_2}) + (\overline{X_3} + \overline{X_4})} = \overline{X_1 \cdot X_2 + X_3 \cdot X_4}.$$

Рис. 25. Карта Карно логической функции «И-ИЛИ-НЕ» из табл. 3.

При количестве входных сигналов более четырёх применение карт Карно для минимизации выражений логических функций оказывается не эффективным. Поскольку среди клеток карты, отличающихся значениями только одного из входных сигналов, оказываются и не соседние, следовательно, возникает необходимость учёта и таких контуров. При этом карта Карно теряет наглядность. На рис. 26 представлена карта Карно для функций пяти входных сигналов. Здесь условия склеивания выполняются также и для клеток, кодировка которых отличается значениями одного из входных сигналов, но не расположенных рядом, а именно клеток, которые симметричны относительно жирной горизонтальной линии. При этом полученное выражение для такого контура имеет следующий вид:  $X_2 \cdot X_3 \cdot \overline{X_4} \cdot X_5$ .

Рис. 26. Карта Карно для функции пяти входных сигналов

## 2.7.4. СИНТЕЗ КОМБИНАЦИОННЫХ СХЕМ НА ЛОГИЧЕСКИХ ЭЛЕМЕНТАХ «И-НЕ» И «ИЛИ-НЕ»

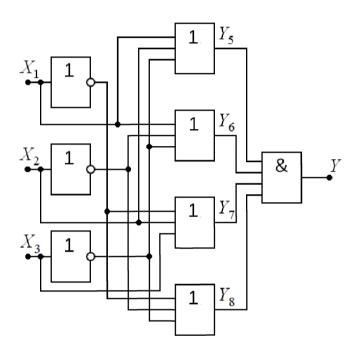

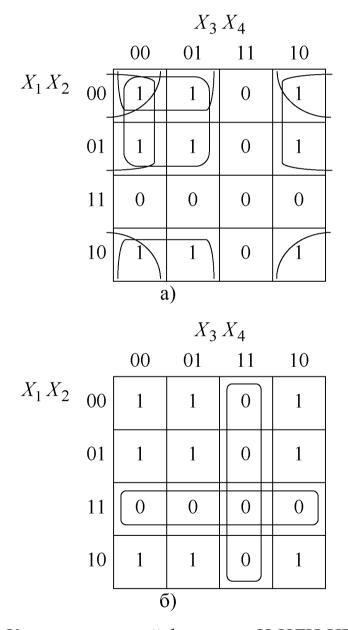

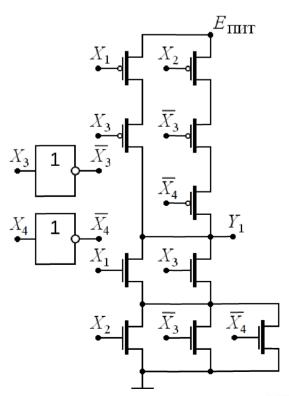

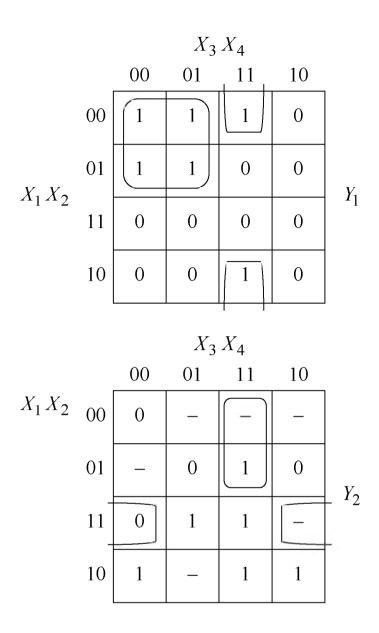

Рассмотрим комбинационные схемы, заданные логическими функциями в табл. 6. Карты Карно представлены на рис. 27.

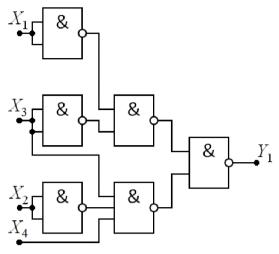

Для  $Y_1$  имеем два контура:

$$Y_1 = \overline{X_1} \cdot \overline{X_3} + \overline{X_2} \cdot X_3 \cdot X_4,$$

применим тождество двойного отрицания и закон отрицания или двойственности (правила де Моргана):

$$Y_1 = \overline{\overline{Y_1}} = \overline{\overline{X_1} \cdot \overline{X_3}} + \overline{\overline{X_2} \cdot \overline{X_3} \cdot \overline{X_4}} = \overline{\overline{X_1} \cdot \overline{X_3}} \cdot \overline{\overline{X_2} \cdot \overline{X_3} \cdot \overline{X_4}},$$

получим выражение для реализации комбинационной схемы на логических элементах «И-НЕ». Схемная реализация для этого выражения показана на рис. 28.

Таблица 6 **Таблица истинности логических функций**

| $X_1$ | $X_2$ | $X_3$ | $X_4$ | $Y_1$ | $Y_2$ |

|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 0     | 1     | 0     |

| 0     | 0     | 0     | 1     | 1     | _     |

| 0     | 0     | 1     | 0     | 0     | _     |

| 0     | 0     | 1     | 1     | 1     | _     |

| 0     | 1     | 0     | 0     | 1     | _     |

| 0     | 1     | 0     | 1     | 1     | 0     |

| 0     | 1     | 1     | 0     | 0     | 0     |

| 0     | 1     | 1     | 1     | 0     | 1     |

| 1     | 0     | 0     | 0     | 0     | 1     |

| 1     | 0     | 0     | 1     | 0     | _     |

| 1     | 0     | 1     | 0     | 0     | 1     |

| 1     | 0     | 1     | 1     | 1     | 1     |

| 1     | 1     | 0     | 0     | 0     | 0     |

| 1     | 1     | 0     | 1     | 0     | 1     |

| 1     | 1     | 1     | 0     | 0     |       |

| 1     | 1     | 1     | 1     | 0     | 1     |

Для  $Y_2$  имеем два контура:

$$Y_2 = (X_1 + X_3) \cdot (\overline{X_2} + X_4),$$

применим тождество двойного отрицания и закон отрицания или двойственности (правила де Моргана):

$$Y_2 = \overline{\overline{Y_2}} = \overline{(X_1 + X_3) \cdot (\overline{X_2} + X_4)} = \overline{\overline{X_1 + X_3} + \overline{X_2} + \overline{X_4}},$$

получим выражение для реализации комбинационной схемы на логических элементах «ИЛИ-НЕ». Схемная реализация для этого выражения показана на рис. 29.

Рис. 27. Карты Карно для табл. 6

Рис. 28. Схема на логических элементах «И-НЕ»

Рис. 29. Схема на логических элементах «ИЛИ-НЕ»

## 2.7.5. СИНТЕЗ КОМБИНАЦИОННЫХ СХЕМ НА ЛОГИЧЕСКИХ ЭЛЕМЕНТАХ «ИЛИ-И-НЕ» И «И-ИЛИ-НЕ»

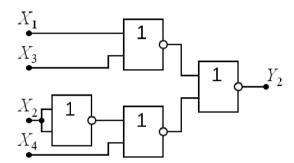

Рассмотрим комбинационные схемы, заданные логическими функциями в табл. 6. Карты Карно представлены на рис. 27. Для  $Y_1$  имеем два контура:

$$Y_1 = \overline{X_1} \cdot \overline{X_3} + \overline{X_2} \cdot X_3 \cdot X_4,$$

применим тождество двойного отрицания и закон отрицания или двойственности (правила де Моргана):

$$Y_1 = \overline{Y_1} = \overline{\overline{X_1} \cdot \overline{X_3} + \overline{X_2} \cdot \overline{X_3} \cdot \overline{X_4}} = \overline{(X_1 + X_3) \cdot (X_2 + \overline{X_3} + \overline{X_4})}$$

получим выражение для реализации комбинационной схемы на основе логического элемента «ИЛИ-И-НЕ». Рассмотрим выражение под знаком инверсии (операции «НЕ»). Логическая сумма (операция «ИЛИ») соответствует последовательному соединению в той части

схемы, где используются МОП-транзисторы с каналами р-типа, и параллельному соединению, где используются МОП-транзисторы с *n*-типа. Логическое произведение каналами (операция «И») соответствует параллельному соединению в той части схемы, где МОП-транзисторы используются c каналами *p*-типа, И последовательному соединению, где используются МОП-транзисторы с каналами *n*-типа. Схемная реализация для этого выражения показана на рис. 30.

Для не полностью определённой функции  $Y_2$  имеем два контура (недоопределенные клетки доопределяются по своему усмотрению):

$$Y_2 = (X_1 + X_3) \cdot (\overline{X_2} + X_4),$$

применим тождество двойного отрицания и закон отрицания или двойственности (правила де Моргана):

$$Y_2 = \overline{\overline{Y_2}} = \overline{(X_1 + X_3) \cdot (\overline{X_2} + X_4)} = \overline{\overline{X_1} \cdot \overline{X_3} + X_2 \cdot \overline{X_4}},$$

получим выражение для реализации комбинационной схемы на основе логического элемента «И-ИЛИ-НЕ». Схемная реализация для этого выражения показана на рис. 31.

Рис. 30. Схема на логическом элементе «ИЛИ-И-НЕ»

Рис. 31. Схема на логическом элементе «И-ИЛИ-НЕ»

## 2.7.6. СИНТЕЗ КОМБИНАЦИОННЫХ СХЕМ НА МУЛЬТИПЛЕКСОРАХ

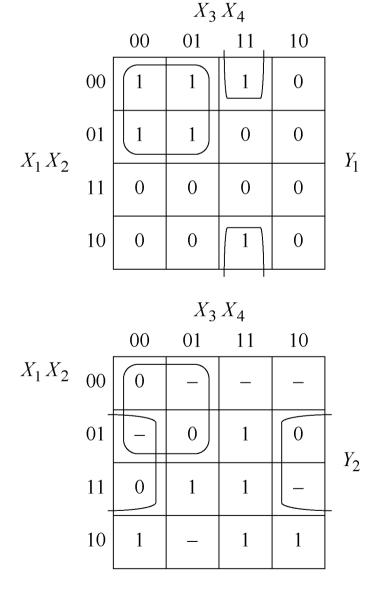

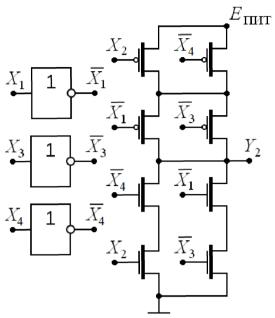

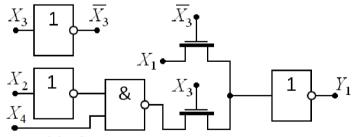

Рассмотрим комбинационные схемы, заданные логическими функциями в табл. 6. Карты Карно представлены на рис. 32. Для  $Y_1$  выбираем в качестве сигнала на адресном входе  $X_3$  и имеем два контура:

$$Y_1 = \overline{X_1} \cdot \overline{X_3} + \overline{X_2} \cdot X_4 \cdot X_3,$$

далее преобразуем:

$$Y_1 = \overline{\overline{X_1}} \cdot \overline{X_3} + \overline{\overline{X_2}} \cdot \overline{X_4} \cdot \overline{X_3} = \overline{X_1} \cdot \overline{X_3} + \overline{\overline{X_2}} \cdot \overline{X_4} \cdot \overline{X_3},$$

получим выражение для реализации комбинационной схемы на мультиплексоре, где  $X_3$  подаётся на адресный вход. Рассмотрим полученное выражение с учётом знака инверсии (операции «НЕ»). При воздействии напряжением логической единицы на вход  $X_3$  на выходе  $Y_1$  формируется логическое состояние, соответствующее  $\overline{X_2} \cdot X_4$ , а при воздействии напряжением логического нуля на вход  $X_3$  на выходе  $Y_1$  формируется логическое состояние, соответствующее  $\overline{X_1}$ . Схемная реализация для этого выражения на мультиплексоре с дополнительным управлением по стоку или истоку показана на рис. 33.

Рис. 32. Карты Карно для табл. 6 при использовании мультиплексоров

Рис. 33. Схема для  $Y_1$  на мультиплексоре

Для  $Y_2$  выбираем в качестве сигнала на адресном входе  $X_1$  и имеем два контура (см. рис. 32):

$$Y_2 = X_3 \cdot X_4 \cdot \overline{X_1} + (\overline{X_2} + X_4) \cdot X_1,$$

далее преобразуем:

$$Y_2 = \overline{X_3 \cdot X_4} \cdot \overline{X_1} + \overline{\overline{X_2} + X_4} \cdot X_1,$$

получим выражение для реализации комбинационной схемы на мультиплексоре, где  $X_1$  подаётся на адресный вход. Рассмотрим полученное выражение с учётом знака инверсии (операции «НЕ»). При воздействии напряжением логической единицы на вход  $X_1$  на выходе  $Y_2$  формируется логическое состояние, соответствующее  $\overline{X_2} + X_4$ , а при воздействии напряжением логического нуля на вход  $X_1$  на выходе  $Y_2$  формируется логическое состояние, соответствующее  $X_3 \cdot X_4$ . Схемная реализация для этого выражения на мультиплексоре с дополнительным управлением по стоку или истоку показана на рис. 34.

Рис. 34. Схема для  $Y_2$  на мультиплексоре

## 2.8. СУММАТОРЫ

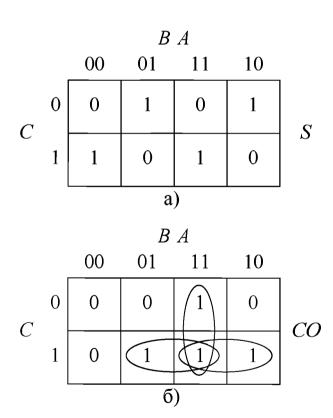

Одноразрядный двоичный сумматор является одним из основных компонентов цифровых интегральных схем, имеет входы A, B — сигналов двух слагаемых, C — сигнала переноса из предыдущего разряда и выходы S — суммы, CO — переноса в следующий разряд. Таблица истинности представлена в табл. 7. На рис. 35 согласно табл. 7 показаны карты Карно для логических функций S и CO (рис. 35,  $\delta$ ) одноразрядного двоичного сумматора. В карте рис. 35,  $\alpha$  для логической функций S отсутствуют контура склеивания, что не позволяет провести минимизацию логического выражения. Минимизированное выражение логической функции CO в виде суммы произведений согласно карте рис. 35,  $\delta$  имеет вид:

$$CO = A \cdot C + B \cdot C + A \cdot B$$

.

Таблица 7 **Таблица истинности одноразрядного двоичного сумматора**

| C           | В | $\boldsymbol{A}$ | S | CO |

|-------------|---|------------------|---|----|

| 0           | 0 | 0                | 0 | 0  |

| 0           | 0 | 1                | 1 | 0  |

| 0           | 1 | 0                | 1 | 0  |

| 0           | 1 | 1                | 0 | 1  |

| $\boxed{1}$ | 0 | 0                | 1 | 0  |

| 1           | 0 | 1                | 0 | 1  |

| 1           | 1 | 0                | 0 | 1  |

| 1           | 1 | 1                | 1 | 1  |

Рис. 35. Карты Карно для логических функции одноразрядного двоичного сумматора из табл. 6.

Для минимизации выражения логической функции S составим таблицу истинности табл. 8, учитывающую сигнал CO, как ещё один входной сигнал. При этом в полученной таблице в столбце S определены восемь значений сигнала суммы согласно табл. 7, а

строки, отмеченные символом «—», физически не реализуемы, поскольку таких сочетаний сигналов *CO*, *C*, *B* и *A* не может быть по правилу работы двоичного сумматора. То есть символ «—» следует рассматривать как неопределённое состояние (либо 0, либо 1), при этом схема сумматора никогда не окажется в состоянии, когда возможно наблюдать такую совокупность выходного сигнала переноса в следующий разряд и трёх входных сигналов, как указано в этих строках таблицы истинности. Таким образом, сигнал суммы имеет вид не полностью определённой логической функции.

Таблица 8

Таблица истинности сигнала суммы одноразрядного двоичного сумматора

| CO | C | B | $\overline{A}$ | S |

|----|---|---|----------------|---|

| 0  | 0 | 0 | 0              | 0 |

| 0  | 0 | 0 | 1              | 1 |

| 0  | 0 | 1 | 0              | 1 |

| 0  | 0 | 1 | 1              | _ |

| 0  | 1 | 0 | 0              | 1 |

| 0  | 1 | 0 | 1              | _ |

| 0  | 1 | 1 | 0              | _ |

| 0  | 1 | 1 | 1              | _ |

| 1  | 0 | 0 | 0              | _ |

| 1  | 0 | 0 | 1              | _ |

| 1  | 0 | 1 | 0              | _ |

| 1  | 0 | 1 | 1              | 0 |

| 1  | 1 | 0 | 0              | _ |

| 1  | 1 | 0 | 1              | 0 |

| 1  | 1 | 1 | 0              | 0 |

| 1  | 1 | 1 | 1              | 1 |

На рис. 36 согласно табл. 8 показана карта Карно для логической функций S одноразрядного двоичного сумматора.

Предполагается, что входящие в контура склеивания символы «—» принимают значения логической единицы. Тогда минимизированное выражение логической функции S в виде суммы произведений согласно карте рис. 36 имеет вид:

$$S = A \cdot \overline{CO} + B \cdot \overline{CO} + C \cdot \overline{CO} + A \cdot B \cdot C.$$

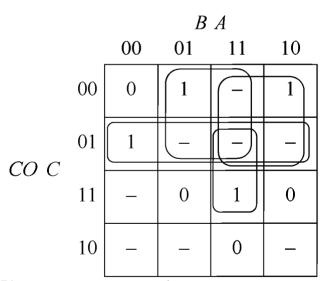

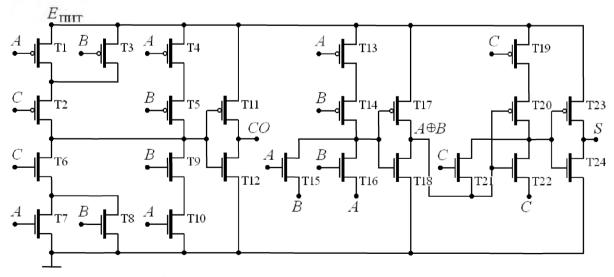

многообразия Среди решений, схемотехнических ориентированных на комплементарные транзисторы, наибольшее распространение получила схема одноразрядного двоичного [2]рис. 37. сумматора Схема показанная на содержит транзисторов, из которых 14 транзисторов Т6-Т10, Т12, Т17-Т20, T24–T26, T28 с каналом *n*-типа и симметрично 14 транзисторов T1– T5, T11, T13-T16, T21-T23, T27 с каналом *p*-типа. Сигнал суммы формируется цепью транзисторов Т13-Т28 с использованием сигнала из цепи переноса на транзисторах Т1-Т12:

$$CO = (A + B) \cdot C + A \cdot B,$$

$S = (A + B + C) \cdot \overline{CO} + A \cdot B \cdot C.$

Рис. 36. Карта Карно логической функции суммы одноразрядного двоичного сумматора из табл. 7.

Повышенного быстродействия одноразрядного двоичного сумматора можно достичь за счёт использования схемы рис. 38, которая состоит из отдельных цепей формирования выходных сигналов суммы и переноса. Данное схемное решение содержит 24

транзистора, по 12 транзисторов с каналом *п*-типа и *p*-типа. Цепь сигнала переноса аналогична рис. 37 и реализована на транзисторах T1–T12. Цепь сигнала суммы в схеме рис. 38 содержит транзисторы T13–T24. Уменьшение времени задержки формирования сигнала суммы обеспечивается схемным решением, не требующим сигнала из цепи переноса и состоящим из последовательного соединения двух ячеек «исключающего ИЛИ» (рис. 21) – первой на транзисторах T13–T18 и второй на транзисторах T19–T24. Учитывая изложенное, выходной сигнал суммы определяется выражением:

$$S = \overline{C} \cdot (A \oplus B) + C \cdot \overline{A \oplus B},$$

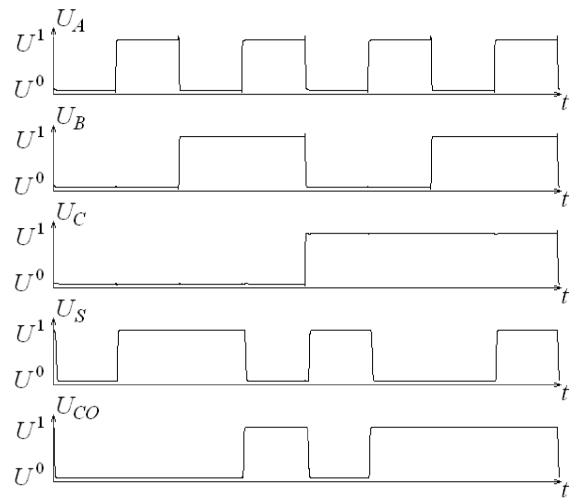

что соответствует таблице истинности (табл. 7). Вид сигналов в схеме сумматора во временной области показан на рис. 39.

Рис. 37. Сумматор на 28 транзисторах

Рис. 38. Сумматор с повышенным быстродействием

Рис. 39. Временные диаграммы работы сумматора

## 2.9. ВОПРОСЫ ДЛЯ САМОПРОВЕРКИ

- 1. Поясните построение эквивалентной схемы по постоянному току комплементарного инвертора. Чем будут отличаться эквивалентные схемы по постоянному и переменному току?

- 2. Объясните процессы заряда и разряда нагрузочной ёмкости комплементарного инвертора. Чем характеризуется запас помехоустойчивости комплементарного инвертора?

- 3. Объясните передаточную характеристику комплементарного инвертора. Как работают транзисторы схемы на горизонтальных и наклонном участках характеристики? Поясните причину появления сквозного тока в цифровых схемах.

- 4. Составьте таблицу истинности логической функции  $Y = X_1 \cdot \overline{X_2} \oplus (\overline{X_3} + X_4)$ . Постройте временные диаграммы работы схемы, реализующей данную логическую функцию.

- 5. Преобразуйте логические функции к более простому виду  $Y_1 = (X_1 + X_2) \cdot (X_1 + \overline{X_2}), \ Y_2 = X_1 \cdot X_2 \cdot X_3 + X_1 \cdot \overline{X_2 \cdot X_3}$ .

- 6. Постройте на логических элементах схему, реализующую логическую функцию  $Y = \overline{X_1 \cdot X_2 \cdot X_3} + X_1 \cdot \overline{X_2} \cdot \overline{X_3}$ .

- 7. Постройте на транзисторном уровне схему, реализующую логическую функцию  $Y = \overline{X_1 \cdot \overline{X_2 \cdot X_3} + \overline{X_1} \cdot \overline{X_2} \cdot \overline{X_3}}$  .

- 8. Объясните переход от таблицы истинности к выражению логической функции в виде СДНФ и СКНФ.

- 9. Как проводится минимизация выражений логических функций по методу Куайна? В чем сложность применения данного метода?

- 10. Как проводится минимизация выражений логических функций на основе карт Карно (в том числе для не полностью определённых логических функций)? В чем заключаются ограничения использования данного метода?

## 3. ПОСЛЕДОВАТЕЛЬНОСТНЫЕ ЦИФРОВЫЕ СХЕМЫ

#### 3.1. ОСОБЕННОСТИ И СПОСОБЫ ОПИСАНИЯ

У последовательностных цифровых схем состояние выхода определяется не только входными сигналами, но и предыдущими состояниями. То есть данные схемы реализуют функциональную связь не между отдельными наборами входных и выходных сигналов, между ИΧ последовательностями В времени моменты  $\dots$ , n-1, n, n+1,  $\dots$ , определяемые синхронно тактовому сигналу. Поэтому последовательностные схемы содержат элементы памяти, информацию 0 сохраняют состояниях сигналов предыдущие моменты времени (на предыдущих тактах). В качестве памяти используются триггеры. Помимо триггеров элементов представителями последовательностных характерными являются регистры и счётчики импульсов [2, 3, 5–10]. Методы синтеза таких схем рассмотрены в работах [3, 5–7, 9].

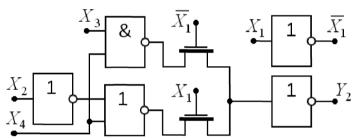

В качестве примера рассмотрим последовательностный двоичный сумматор, который осуществляет логическое сложение двух сигналов, поступающих на его входы последовательно разряд за разрядом синхронно тактовому сигналу, начиная с младших разрядов. На каждом такте схема определяет логическое значение сигнала суммы для текущего разряда с учётом сохранённой информации о значении сигнала переноса из предыдущего разряда и сохраняет значение сигнала переноса для следующего разряда. При этом информация о текущем значении сигнала переноса сохраняется только на один такт и обновляется с каждым следующим тактом.

В соответствии с представленным описанием последовательностный двоичный сумматор имеет два входных сигнала  $X_1$  и  $X_2$ , выходной сигнал суммы Y и элемент памяти для хранения сигнала переноса Z. Множество состояний сигналов входов такой схемы состоит из четырёх элементов:

$$\{X_1X_2\} = \{00,01,11,10\}.$$

Состояний, как сигналов выхода суммы, так и сигналов переноса имеется по два:

$$\{Y\} = \{Y_1 = 0, Y_2 = 1\}, \{Z\} = \{Z_1 = 0, Z_2 = 1\}.$$

Функционирование двухвходового последовательностного двоичного сумматора может быть представлено таблицей переключений в виде табл. 9, где индексы n и n+1 указывают на значения сигналов на текущем и следующем тактах соответственно.

Таблица 9

Таблица переключений двухвходового последовательностного сумматора

| $X_1^n$ | $X_2^n$ | $Z^n$ | $Y^n$ | $Z^{n+1}$ |

|---------|---------|-------|-------|-----------|

| 0       | 0       | 0     | 0     | 0         |

| 0       | 0       | 1     | 1     | 0         |

| 0       | 1       | 0     | 1     | 0         |

| 0       | 1       | 1     | 0     | 1         |

| 1       | 0       | 0     | 1     | 0         |

| 1       | 0       | 1     | 0     | 1         |

| 1       | 1       | 0     | 0     | 1         |

| 1       | 1       | 1     | 1     | 1         |

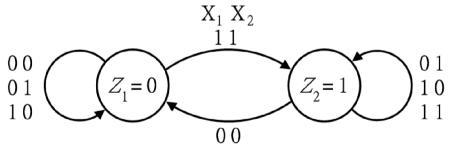

таблиц переключений Помимо ДЛЯ описания последовательностных схем используются таблицы состояний и переходов. На рис. 40 показана таблица состояний и переходов двухвходового последовательностного двоичного сумматора. Первая строка таблицы описывает функционирование схемы при воздействии на текущем такте всех возможных состояний входных сигналов, если сигнал переноса при сложении на предыдущем такте оказался равным логическому нулю. В каждой клетке указаны получаемые в результате сигналы выхода суммы и переноса. Вторая строка таблицы описывает функционирование схемы, если сигнал переноса при на предыдущем такте оказался равным логической сложении

единице. Например, при  $Z^n=Z_2=1$  (вторая строка таблицы) в результате воздействия входных сигналов  $X_1^n=0$  и  $X_2^n=0$  (первый столбец) получаем сигнал выхода суммы  $Y^n=Y_2=1$  и сигнал переноса для следующего разряда  $Z^{n+1}=Z_1=0$ .

$$X_1 X_2$$

$$00 01 11 10$$

$$Z_1 = 0 Y_1 = 0, Z_1 = 0 Y_2 = 1, Z_1 = 0 Y_1 = 0, Z_2 = 1 Y_2 = 1, Z_1 = 0$$

$$Z_2 = 1 Y_2 = 1, Z_1 = 0 Y_1 = 0, Z_2 = 1 Y_2 = 1, Z_2 = 1 Y_1 = 0, Z_2 = 1$$

Рис. 40. Таблица состояний и переходов двухвходового последовательностного двоичного сумматора

Функционирование последовательностных схем может быть проиллюстрировано графом состояний и переходов (рис. 41), который фактически является наглядным аналогом таблицы состояний и переходов (рис. 40). При этом граф позволяет проводить анализ на наличие зацикливаний при функционировании последовательностных графа схем. В случае двухвходового последовательностного двоичного сумматора, показанного рис. 41, зацикливания на отсутствуют.

Рис. 41. Граф состояний и переходов двухвходового последовательностного двоичного сумматора

## 3.2. ТРИГГЕРЫ С ПОТЕНЦИАЛЬНЫМ УПРАВЛЕНИЕМ

Общим свойством триггеров является сохранение одного из двух устойчивых состояний после прекращения воздействия входных

сигналов. Триггер имеет два выхода: прямой Q и инверсный Q. Уровнями напряжения на этих выходах определяется состояние, в котором находится триггер. Если напряжение на прямом выходе соответствует логическому нулю, то считается, что триггер находится в состоянии логического нуля, в другом случае - триггер находится в состоянии логической единицы. Входные сигналы для управления быть триггерами ΜΟΓΥΤ В виде постоянного напряжения, соответствующего либо логическому нулю, либо логической единице. Такие триггеры являются схемами с потенциальным управлением, или асинхронным. Асинхронность означает, что устройства могут менять состояние в произвольные моменты времени, в отличие от синхронных, которые меняют состояние только в моменты времени, задаваемые тактовым сигналом. В англоязычной литературе такие триггеры называются latch – защёлки.

#### 3.2.1. *RS*-ТРИГГЕРЫ

Базовым типом триггера является *RS*-триггер. На его основе строятся остальные триггеры, при этом самостоятельно (не в составе В триггера) данный триггер современной цифровой другого используется. не RS-триггер интегральной схемотехнике переключающими сигналами уровня логической единицы имеет два входа и работает следующим образом. Если сигналы на обоих входах соответствуют логическому нулю, то триггер не изменяет своего состояния и находится в режиме хранения; если на вход установки S(Set) подаётся логическая единица, а на вход сброса R (Reset) – логический нуль, то триггер устанавливается в состояние логической единицы; если на вход S подаётся логический нуль, а на вход R – логическая единица, то триггер сбрасывается в состояние логического нуля; одновременное воздействие логической единицы по обоим входам должно быть исключено, считается, что такое состояние входных сигналов должно быть запрещено (запрещённое состояние). Работу данного триггера можно представить в виде таблицы переключений табл. 10, при одновременном воздействии логической единицы по обоим входам  $Q = \overline{Q} = 0$ , что противоречит пониманию прямого и инверсного выходов.

Таблица 10 Таблица переключений *RS*-триггера с переключающими сигналами уровня логической единицы

| $R^n$          | $S^n$ | $Q^n$     | $\overline{Q}^n$     |

|----------------|-------|-----------|----------------------|

| 0              | 0     | $Q^{n-1}$ | $\overline{Q^{n-1}}$ |

| 0              | 1     | 1         | 0                    |

| $\overline{1}$ | 0     | 0         | _ 1                  |

| 1              | 1     | 0         | 0                    |

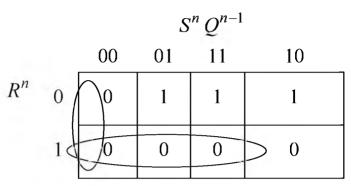

Для минимизации выражения логической функции  $Q^n$  составим таблицу истинности табл. 11, учитывающую сигнал  $Q^{n-1}$ , как дополнительный входной сигнал. На рис. 42 согласно табл. 11 показана карта Карно для логической функции  $Q^n$ . Минимизированное выражение имеет вид:

$$Q^{n} = \overline{R^{n}} \cdot (S^{n} + Q^{n-1}) = \overline{R^{n}} \cdot (S^{n} + Q^{n-1}) = \overline{R^{n} + (S^{n} + Q^{n-1})}.$$

Таблица 11 Таблица переключений сигнала  $Q^n$  RS-триггера с переключающими сигналами уровня логической единицы

| $R^n$ | $S^n$ | $Q^{n-1}$ | $Q^n$ |

|-------|-------|-----------|-------|

| 0     | 0     | 0         | 0     |

| 0     | 0     | 1         | 1     |

| 0     | 1     | 0         | 1     |

| 0     | 1     | 1         | 1     |

| 1     | 0     | 0         | 0     |

| 1     | 0     | 1         | 0     |

| 1     | 1     | 0         | 0     |

| 1     | 1     | 1         | 0     |

Рис. 42. Карта Карно логической функции  $Q^n$  из табл. 11.

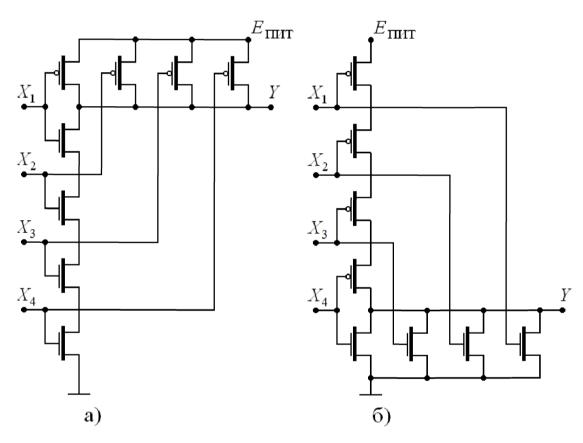

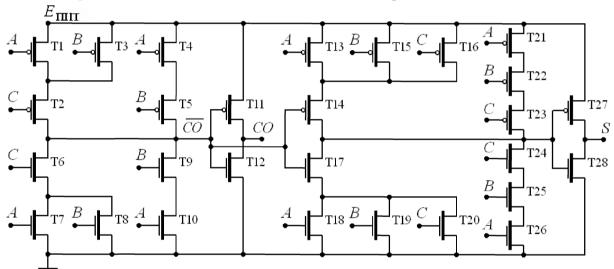

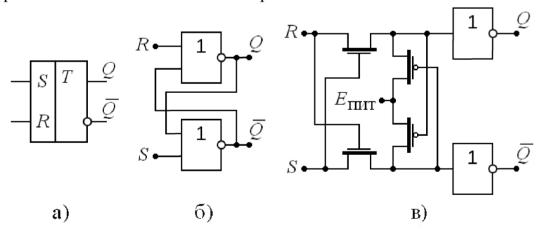

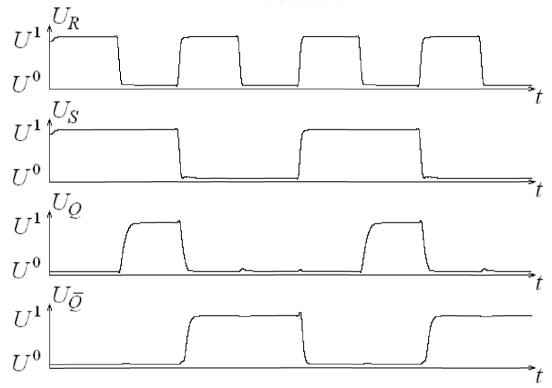

Таким образом, схема RS-триггера с переключающими сигналами уровня логической единицы строится на основе двух двухвходовых логических элементов «ИЛИ-НЕ» (рис. 9,  $\delta$  и рис. 9,  $\epsilon$ ). Обозначение RS-триггера с переключающими сигналами уровня логической единицы показано на рис. 43,  $\alpha$ , схема представлена на рис. 43,  $\delta$ . Схема RS-триггера с переключающими сигналами уровня логической единицы на проходных транзисторах с дополнительным управлением по стоку и истоку показана на рис. 43,  $\delta$ . Вид сигналов во временной области показан на рис. 44.

Рис. 43. *RS*-триггер с переключающими сигналами уровня логической единицы

RS-триггер может быть синтезирован с переключающими сигналами уровня логического нуля, тогда схема работает следующим образом. Если сигналы на обоих входах соответствуют логической единице, то триггер не изменяет своего состояния и находится в режиме хранения; если на вход установки S подаётся логический нуль, а на вход сброса R — логическая единица, то триггер

устанавливается в состояние логической единицы; если на вход S подаётся логическая единица, а на вход R — логический нуль, то триггер сбрасывается в состояние нуля; одновременное воздействие логического нуля по обоим входам следует исключить, считается, что такое состояние входных сигналов должно быть запрещено (запрещённое состояние). Работу триггера можно представить в виде таблицы переключений табл. 12, при одновременном воздействии логического нуля по обоим входам  $O = \overline{O} = 1$ .

Рис. 44. Временные диаграммы работы *RS*-триггера с переключающими сигналами уровня логической единицы

Таблица 12 Таблица переключений *RS*-триггера с переключающими сигналами уровня логического нуля

| $R^n$ | $S^n$ | $Q^n$     | $\overline{Q}^n$     |

|-------|-------|-----------|----------------------|

| 0     | 0     | 1         | 1                    |

| 0     | 1     | 0         | 1                    |

| 1     | 0     | 1         | 0                    |

| 1     | 1     | $Q^{n-1}$ | $\overline{Q^{n-1}}$ |

Для минимизации выражения логической функции  $Q^n$  составим таблицу истинности табл. 13, учитывающую сигнал  $Q^{n-1}$ , как дополнительный входной сигнал. На рис. 45 согласно табл. 13 показана карта Карно для логической функции  $Q^n$ . Минимизированное выражение имеет вид:

$$Q^n = \overline{S^n} + R^n \cdot Q^{n-1} = \overline{S^n + R^n \cdot Q^{n-1}} = \overline{S^n \cdot \overline{R^n \cdot Q^{n-1}}}.$$

Таблица 13

Таблица переключений сигнала  $Q^n$  RS-триггера с переключающими сигналами уровня логического нуля

| $R^n$ | $S^n$ | $Q^{n-1}$ | $Q^n$ |

|-------|-------|-----------|-------|

| 0     | 0     | 0         | 1     |

| 0     | 0     | 1         | 1     |

| 0     | 1     | 0         | 0     |

| 0     | 1     | 1         | 0     |

| 1     | 0     | 0         | 1     |

| 1     | 0     | 1         | 1     |

| 1     | 1     | 0         | 0     |

| 1     | 1     | 1         | 1     |

|       |   | $S^n Q^{n-1}$ |    |    |    |

|-------|---|---------------|----|----|----|

|       |   | 00            | 01 | 11 | 10 |

| $R^n$ | 0 | 1             | 1  | 0  | 0  |

|       | 1 | 1             | 1  | 1) | О  |

Рис. 45. Карта Карно логической функции  $Q^n$  из табл. 13.

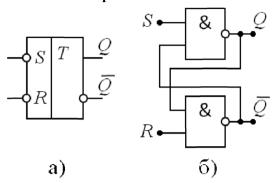

Схема RS-триггера с переключающими сигналами уровня логического нуля строится на основе двух двухвходовых логических элементов «И-НЕ» (рис. 9, a и рис. 9, b). Обозначение RS-триггера с переключающими сигналами уровня логического нуля, показано на

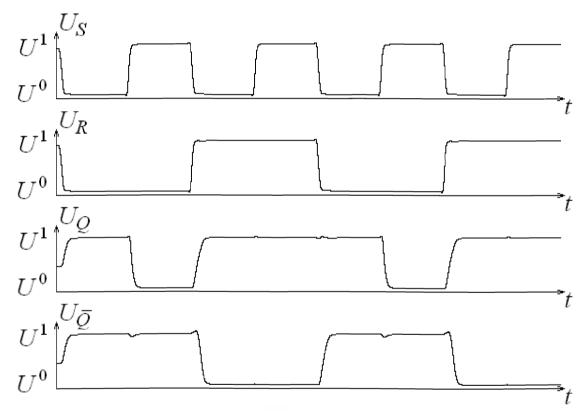

рис. 46, a, схема представлена на рис. 46,  $\delta$ . Вид сигналов в схеме во временной области показан на рис. 47.

Рис. 46. *RS*-триггер с переключающими сигналами уровня логического нуля

Рис. 47. Временные диаграммы работы *RS*-триггера с переключающими сигналами уровня логического нуля

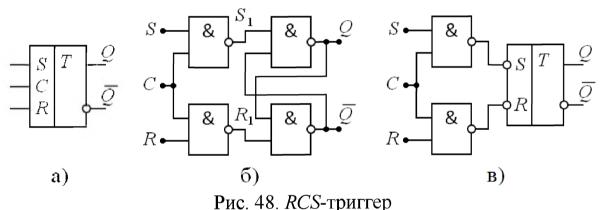

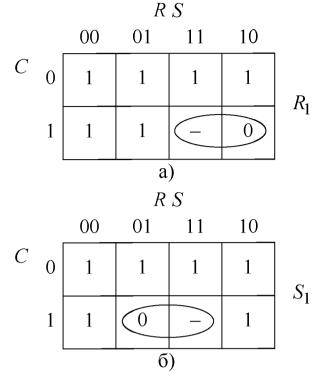

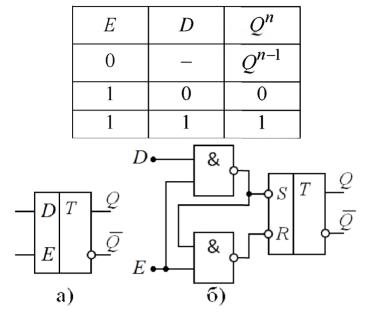

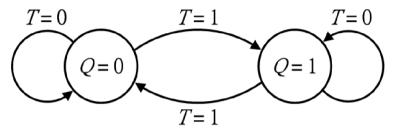

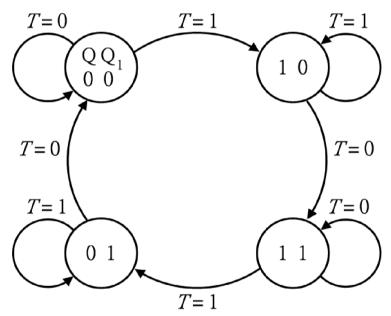

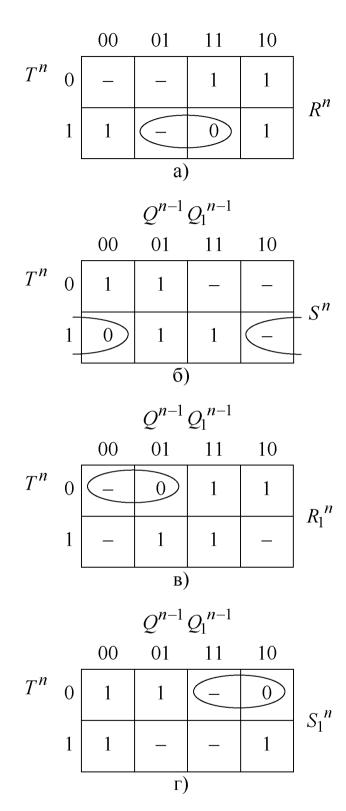

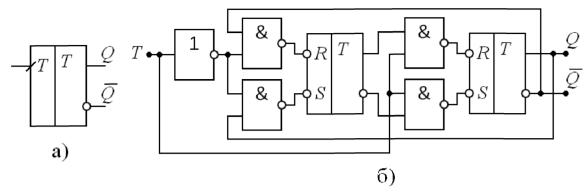

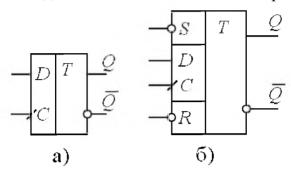

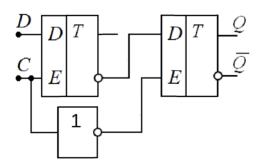

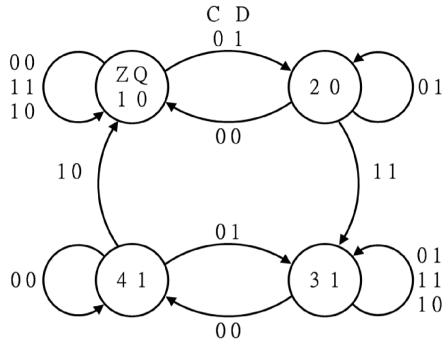

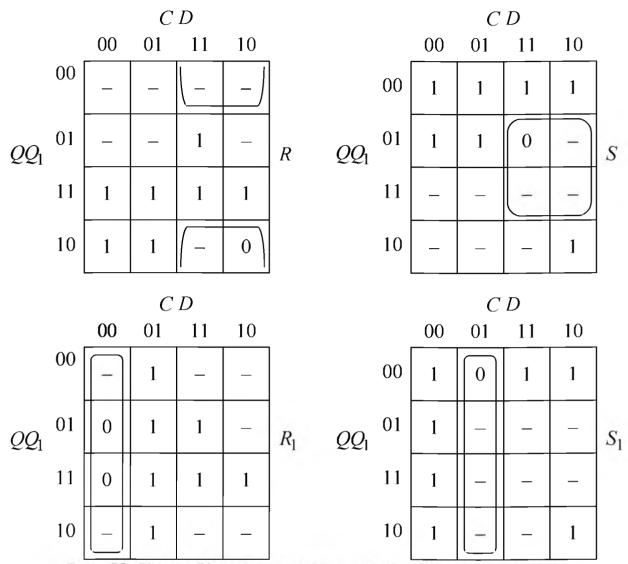

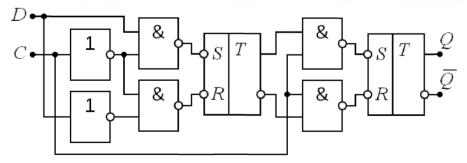

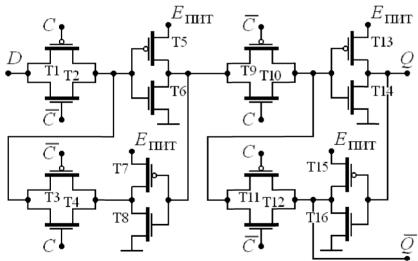

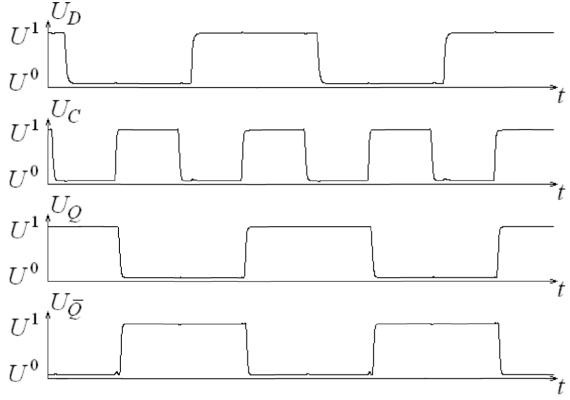

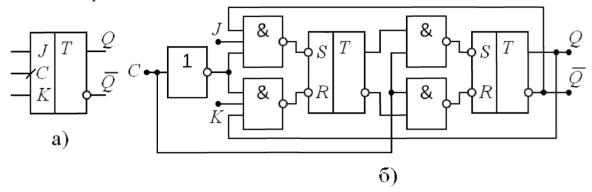

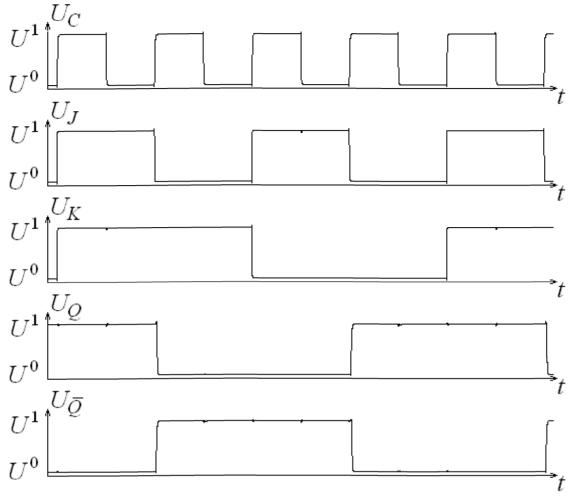

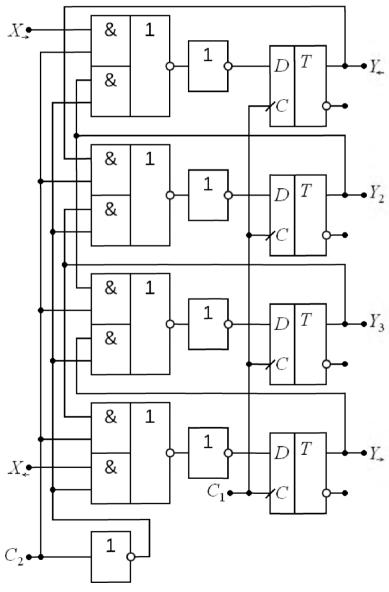

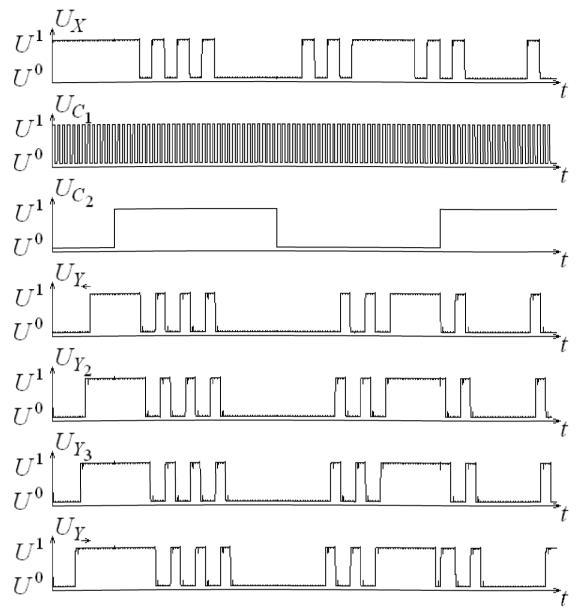

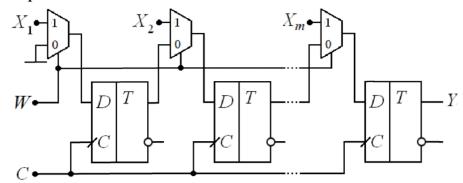

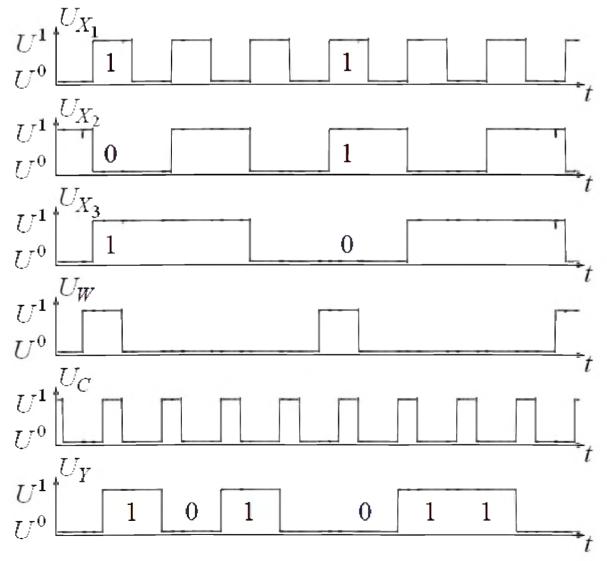

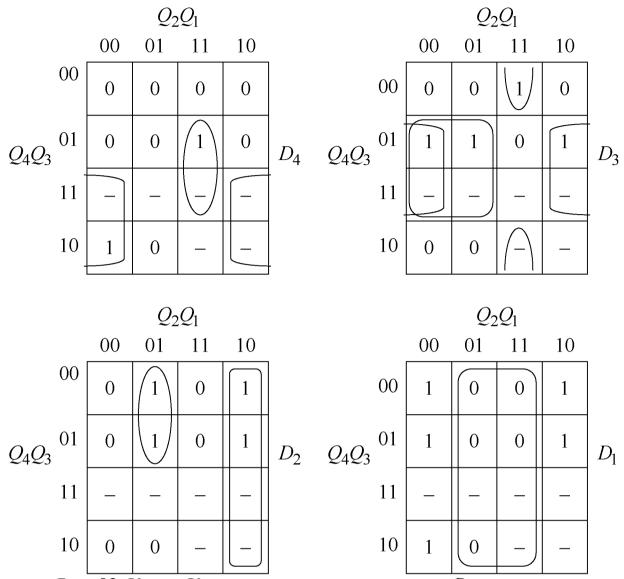

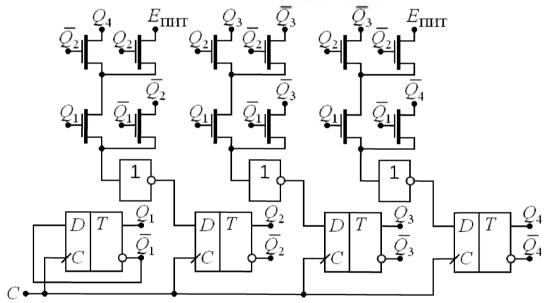

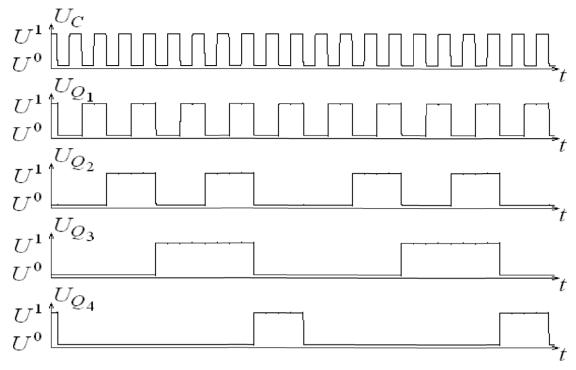

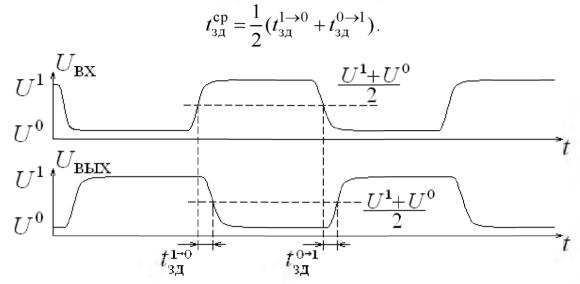

#### 3.2.2. *RCS*-ТРИГГЕР